## **Supplementary Information**

for

Surface grafting of octylamine onto poly(ethylene-*alt*-maleic anhydride) gate insulators for low-voltage DNTT thin-film transistors

Yun-Seo Choe,<sup>ab</sup> Mi Hye Yi,<sup>a</sup> Ji-Heung Kim,<sup>b</sup> Yun Ho Kim,\*a and Kwang-Suk Jang\*a

<sup>a</sup>Division of Advanced Materials, Korea Research Institute of Chemical Technology, Daejeon 34114, Republic of Korea. E-mail: kjang@krict.re.kr, yunho@krict.re.kr

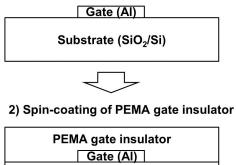

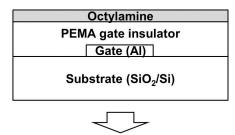

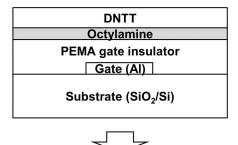

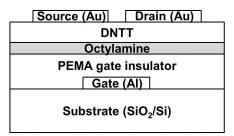

<sup>b</sup>School of Chemical Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea 1) AI deposition using thermal evaporation

Substrate (SiO<sub>2</sub>/Si)

3) Octylamine treatment by spin-coating

4) DNTT deposition using thermal evaporation

5) DNTT deposition using thermal evaporation

Fig. S1 Scheme of the TFT device fabrication.

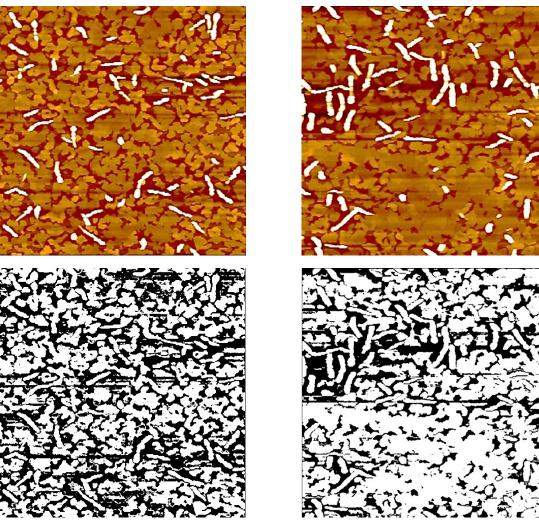

## non-treated

→  $100 - 49.544 = 50.467 \ \mu m^2$

→ 100 – 30.711 = 69.289  $\mu$ m<sup>2</sup>

octylamine-treated

| 🛓 Results              |        |      |     |     |        |        |          |

|------------------------|--------|------|-----|-----|--------|--------|----------|

| File Edit Font Results |        |      |     |     |        |        |          |

|                        | Area   | Mean | Min | Мах | MinThr | MaxThr | <u> </u> |

| 1                      | 49.533 | 255  | 255 | 255 | 9      | 255    |          |

| 2                      | 30.711 | 255  | 255 | 255 | 255    | 255    |          |

|                        |        |      |     |     |        |        |          |

|                        |        |      |     |     |        |        |          |

|                        |        |      |     |     |        |        |          |

|                        |        |      |     |     |        |        |          |

|                        |        |      |     |     |        |        |          |

| •                      |        |      |     |     |        |        |          |

**Fig. S2** The surface coverage measurement of the 12 nm-thick DNTT layers on non-treated and octylamine-treated PEMA thin films.

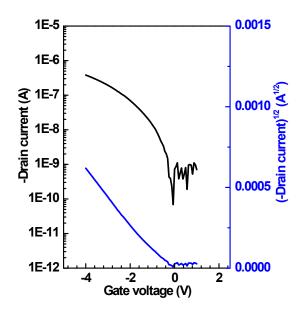

**Fig. S3** Transfer characteristic ( $I_{ds}$  vs.  $V_{gs}$ ) of the DNTT TFTs with the 60 nm-thick SiO<sub>2</sub> gate insulator.