Supplementary Information:

## Low voltage and high ON/OFF ratio field-effect

## transistors based on CVD MoS<sub>2</sub> and ultra high-k PZT

## gate dielectric

Changjian Zhou,<sup>ab</sup> Xinsheng Wang,<sup>a</sup> Salahuddin Raju,<sup>b</sup> Ziyuan Lin,<sup>a</sup> Daniel Villaroman,<sup>c</sup> Baoling Huang,<sup>c</sup> Helen Lai-Wa Chan,<sup>a</sup> Mansun Chan<sup>b</sup> and Yang Chai<sup>\*a</sup>

<sup>a</sup> Department of Applied Physics, The Hong Kong Polytechnic University, Kowloon, Hong Kong.

Email:ychai@polyu.edu.hk

<sup>b</sup> Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Kowloon, Hong Kong

c Department of Mechanical and Aerospace Engineering, The Hong Kong University of Science and Technology, Kowloon, Hong Kong

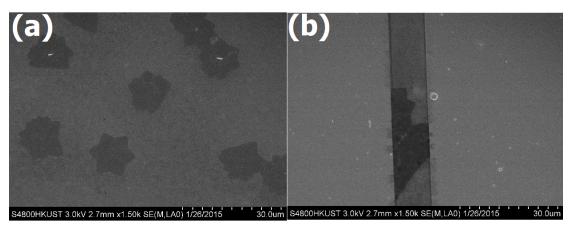

Fig. S1 SEM pictures of the transferred  $MoS_2$  flakes on the PZT substrate. (a) Some triangular  $MoS_2$  flakes are merged during the growth. (b)A typical device with Au/Ti electrodes on a  $MoS_2$  flake.

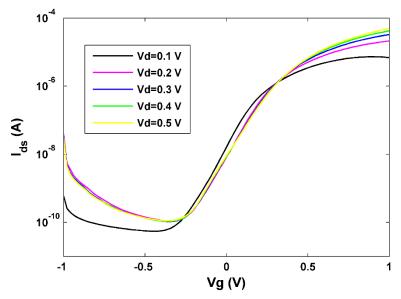

We have fabricated PZT gated MoS<sub>2</sub> transistors with different channel dimensions and presented the transfer characteristics of several devices as following:

a) Electrical characteristics of MoS<sub>2</sub> transistor with L= 2  $\mu$ m and W= 20  $\mu$ m. For this device, V<sub>T</sub>=0.2 V, SS= 104 mV/dec, and  $\mu$ =10.01 cm<sup>2</sup>/V·s.

Fig. S2 Transfer characteristics of a MoS<sub>2</sub> transistor with L= 2  $\mu$ m and W= 20  $\mu$ m.

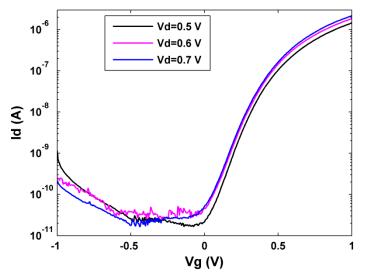

b) MoS<sub>2</sub> transistor with L= 4  $\mu$ m and W= 5  $\mu$ m. For this device, V<sub>T</sub>=0.41 V, SS= 109 mV/dec, and  $\mu$ =6.19 cm<sup>2</sup>/V·s.

Fig. S3 Transfer characteristics of a  $MoS_2$  transistor with L= 4  $\mu$ m and W= 5  $\mu$ m.

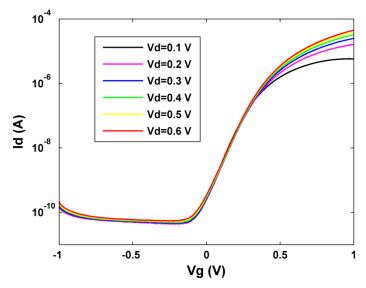

c) Electrical characteristics of MoS<sub>2</sub> transistor with L= 4  $\mu$ m and W= 20  $\mu$ m. For this device, V<sub>T</sub>=0.32 V, SS= 99 mV/dec, and  $\mu$ =3.92 cm<sup>2</sup>/V·s.

Fig. S4 Transfer characteristics of a MoS<sub>2</sub> transistor with L= 4  $\mu$ m and W= 20  $\mu$ m.

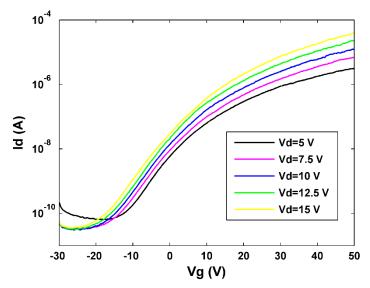

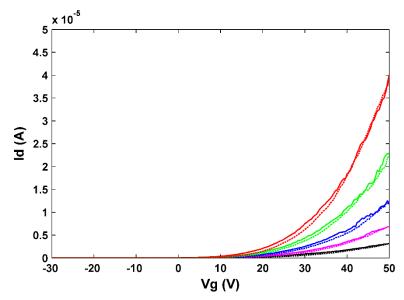

As a reference, the  $MoS_2$  flakes were transferred to a  $SiO_2/Si$  substrate for transistor fabrication and characterization. Fig. S5 shows the transfer characteristics of a  $MoS_2$  transistor with L= 2 µm and W= 100 µm. Fig. S6 shows the hysteresis behavior of the same device. All the electrical characterization was conducted at 300 K in a vacuum probe station.

Fig. S5 Transfer characteristics of a 300 nm SiO<sub>2</sub> gated MoS<sub>2</sub> transistor with L= 2  $\mu$ m and W= 100  $\mu$ m.

Fig. S6 Hysteresis characteristics of a 300 nm SiO<sub>2</sub> gated MoS<sub>2</sub> transistor with L= 2  $\mu$ m and W= 100  $\mu$ m.