## Dynamic Monitoring of Transmembrane Potential Changes: Study of Ion Channels using

## **Electrical Double Layer gated FET Biosensor**

Anil Kumar Pulikkathodi<sup>a</sup>, Indu Sarangadharan<sup>a</sup>, Yi-Hong Chen<sup>b</sup>, Geng-Yen Lee<sup>d</sup>, Jen-Inn Chyi<sup>d</sup>,

Gwo-Bin Lee<sup>a,b,c\*</sup>, and Yu-Lin Wang<sup>a,b\*</sup>

<sup>a</sup> Institute of NanoEngineering and MicroSystems, National Tsing Hua University, Hsinchu,

Taiwan 300, R.O.C.

<sup>b</sup> Department of Power Mechanical Engineering, National Tsing Hua University, Hsinchu,

Taiwan 300, R.O.C.

<sup>c</sup> Institute of Biomedical Engineering, National Tsing Hua University, Hsinchu, Taiwan 300,

R.O.C.

<sup>d</sup> Department of Electrical engineering, National Central University, Jhongli City, Taoyuan

County 320, Taiwan, R.O.C.

\*Correspondence to <u>vlwang@mx.nthu.edu.tw</u>

\*Co-correspondence to <u>gwobin@pme.nthu.edu.tw</u>

## Supplementary Information

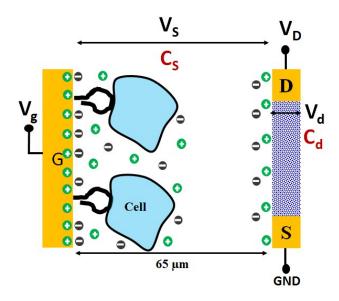

EDL gated FET biosensor structure

The FET sensing region is defined as the gate electrode and channel openings ( $10x60 \ \mu m^2$ ) separated by 65  $\mu m$  which is filled by the test solution. Electrical double layer (EDL) is formed on gate electrode/solution and transistor dielectric/solution interfaces, as shown in Figure S1. When bias is applied to the gate electrode, applied potential drops across the test solution and the

transistor dielectric, because of the charge distribution in the EDL on the gate electrode and dielectric interfaces. This creates a solution capacitance  $C_s$  across the test solution (shown in Figure S1) which modulates the potential drop across the dielectric  $V_d$ .

The overall potential drop can be written as

$$V_g = \Delta V_s + \Delta V_d$$

Equation 1

Where  $V_s$  and  $V_d$  refer to the potential drops across solution and transistor dielectric respectively, and  $V_g$  is the applied gate voltage.

Since impedance in an electrical circuit can be represented as

$$Z = \frac{1}{j\omega C}$$

Equation 2

Where C is the total capacitance in the circuit, which can be written as

$$\frac{1}{C} = \frac{1}{C_S} + \frac{1}{C_d}$$

Equation 3

Where C<sub>s</sub> and C<sub>d</sub> are the solution and dielectric capacitances respectively.

Hence  $V_d$  in equation 1 can be re-written in terms of solution capacitance as

$$\Delta V_d = \frac{\frac{1}{j\omega C_d}}{\frac{1}{j\omega C_d} + \frac{1}{j\omega C_s}} \times V_g = \frac{C_s}{C_d + C_s} \times V_g$$

Equation 4

Where j and  $\omega$  are current and angular frequency, respectively.

The potential drop across the dielectric eventually modulates the channel conductivity and hence the drain current of FET.

Figure S1 Schematic representation of potential drops across EDL gated FET biosensor.

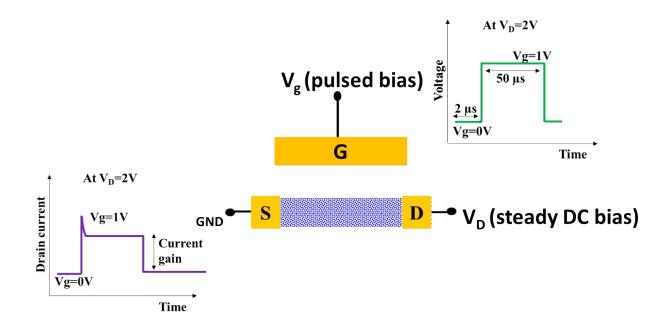

Sensor measurement technique

The gate electrode separated from the FET channel region is supplied with a short duration (50  $\mu$ s), pulsed gate voltage of amplitude 2 V. The applied potential profile is shown in Figure S2. During the first 2  $\mu$ s of measurement, there is no V<sub>g</sub> (gate bias) applied, following which V<sub>g</sub> of 2 V is applied for 50  $\mu$ s. During the measurement, a steady DC bias of 2.5 V is applied as drain voltage. The drain current response is also shown schematically in Figure S2, showing current gain calculations.

Figure S2 Sensor measurement parameters.