Electronic Supplementary Material (ESI) for Journal of Materials Chemistry C. This journal is © The Royal Society of Chemistry 2018

## **Supporting Information**

## Solution-processed ternary p-type CuCrO<sub>2</sub> semiconductor thin films and their application in transistors

Shengbin Nie, a,b,c1 Ao Liu, a,b,c1 You Meng, a,b,c Byoungchul Shin, Guoxia Liu, a,b,c\* and Fukai Shana,b,c\*

<sup>a</sup>College of Physics, Qingdao University, Qingdao 266071, China

<sup>b</sup>College of Electronic & Information Engineering, Qingdao University, Qingdao 266071, China

<sup>c</sup>Lab of New Fiber Materials and Modern Textile, Growing Base for State Key Laboratory,

Qingdao University, Qingdao 266071, China

<sup>d</sup>Electronic Ceramics Center, DongEui University, Busan 614714, Korea

<sup>\*</sup>Corresponding author: <a href="mailto:gxliu@qdu.edu.cn">gxliu@qdu.edu.cn</a>; <a href="fukaishan@yahoo.com">fukaishan@yahoo.com</a>;

S. Nie and A. Liu contributed equally to this work.

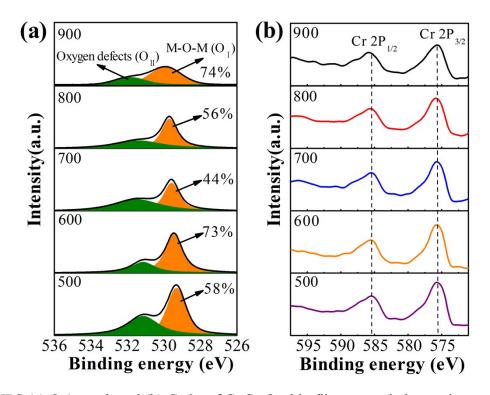

The O 1s binding energies of the CuCr<sub>x</sub>O<sub>y</sub> thin films annealed at various temperatures are shown in Figure S1(a). The O 1s peaks were divided into two peaks centered at 529.5 eV and 531.8 eV, which can be assigned to the lattice oxygen and the oxygen defects (insertion of O<sup>2-</sup> ions herein) in CuCr<sub>x</sub>O<sub>y</sub> thin films,<sup>1</sup> respectively. From the thin films annealed at 500 °C to 600 °C, the lattice oxygen component increases with increasing annealing temperature because the oxygen-related defects are eliminated and the M-O bonds are enhanced with the increase of the annealing temperature.<sup>2</sup> However, the decrease of the lattice oxygen component from 600 °C to 700 °C may be due to the transformation from mixed CuCr<sub>2</sub>O<sub>4</sub> and CuO phase to pure CuCrO<sub>2</sub> phase. This process may be accompanied by the breakdown of the M-O bonds and the release of the oxygen, leading to the decrease of M-O component. Reasonably, the M-O component experienced an increase from 700 °C to 900 °C, resulting from the improvement of CuCrO<sub>2</sub> phase crystallinity.<sup>3</sup>

The Cr  $2p_{1/2}$  and Cr  $2p_{3/2}$  peaks are located at 586.0 and 576.0 eV, respectively. No apparent change of peak position is observed within the whole processing temperatures (Figure S1(b)), suggesting that  $Cr^{3+}$  is maintained during the entire reduction process.

Figure S1. XPS (a) O 1s peak and (b) Cr 2p of CuCr<sub>x</sub>O<sub>y</sub> thin films annealed at various temperatures.

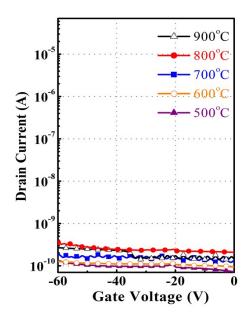

Figure S2. Gate leakage current of the CuCr<sub>x</sub>O<sub>y</sub> TFTs annealed at various temperatures.

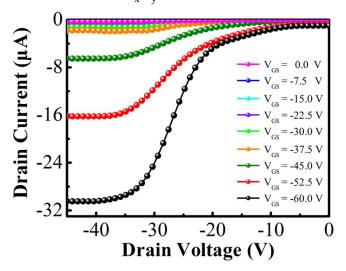

Figure S3. The output curves of CuCrO<sub>2</sub> TFT annealed at 800 °C.

The output curves exhibit the slight current crowding in the low  $V_{\rm DS}$  region and current saturation in the high  $V_{\rm DS}$  region. The current crowding phenomenon indicates the Schottky contact between the electrodes and CuCrO<sub>2</sub> channel layer, although the Ni metal used in this study possesses high work function (>5 eV). In the previous reports on p-type TFTs, such a Schottky contact behaviors were frequently observed even using other metal electrodes (e.g., Au and Ti/Au bilayer).<sup>4-6</sup> The further optimization of electrode materials is required to achieve ideal Ohmic contact and better device performance.

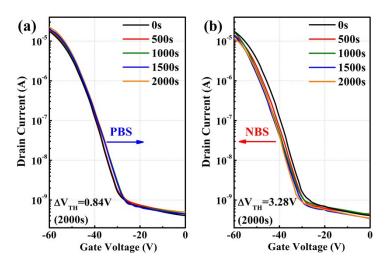

Figure S4. Transfer curves of the CuCrO<sub>2</sub> TFTs annealed at 800°C (a) under PBS tests and (b) NBS tests for 2000 s with a time interval of 500 s.

To clarify the gate-bias-stability of the device, both positive bias stress (PBS) and negative bias stress (NBS) measurements were carried out on the optimized  $CuCrO_2$  TFT by applying a  $V_{GS}$  of  $\pm$  60 V. A maximum  $V_{TH}$  shift of 0.84 and 3.28 V were recorded after PBS and NBS tests for 2000 s. The main mechanism for the  $V_{TH}$  shift is due to the charge trapping effect at the interface.<sup>7</sup> It is noted that the  $I_{on}$  of the device degrades gradually with increasing the bias stress time under NBS, while  $I_{on}$  remains unchanged under PBS tests. For the p-type oxide TFTs, the amount of electrons in channel layers is negligible compared with holes. Under NBS test, the interface states are gradually filled with the increase of the stress time. The trapped holes at  $CuCrO_2$  interface will possibly induce either phonon scattering or Coulomb scattering, leading to the decrease of  $I_{on}$ .<sup>8</sup>

Table S1. Chemical compositions of CuCr<sub>x</sub>O<sub>v</sub> thin films annealed at various temperatures.

| 3.3 |

|-----|

| 3.2 |

| 3.3 |

| 3.1 |

| 3.3 |

| 3.3 |

|     |

## References

- 1. T. Jiang, X. Li, M. Bujoli-Doeuff, E. Gautron, L. Cario, S. Jobic and R. Gautier, *Inorg. Chem.*, 2016, 55, 7729.

- 2. G. Jiang, A. Liu, G. Liu, C. Zhu, Y. Meng, B. Shin, E. Fortunato, R. Martins and F. Shan, *Appl. Phys. Lett.*, 2016, **109**, 183508.

- 3. J. Wang, P. Zheng, X. Zhou and L. Fang, J. Sol-Gel Sci. Technol., 2016, 79, 37.

- 4. S. Liu, R. Liu, Y. Chen, S. Ho, J. H. Kim and F. So, Chem. Mater., 2014, 26, 4528.

- 5. S. Takami, R. Hayakawa, Y. Wakayama and T. Chikyow, *Nanotechnology*, 2010, **21**, 134009.

- 6. J. Jiang, X. Wang, Q. Zhang, J. Li and X. Zhang, *Phys. Chem. Chem. Phys.*, 2013, **15**, 6875.

- 7. I. C. Chiu and I. C. Cheng, *IEEE Electr. Device. L.*, 2014, **35**, 90.

- 8. A. Liu, G. Liu, H. Zhu, B. Shin, E. Fortunato, R. Martins and F. Shan, *Appl. Phys. Lett.*, 2016, **108**, 233506.