## **Supplementary Information**

## **Optical-Reconfigurable Carbon Nanotube and Indium-Tin-Oxide**

## **Complementary Thin-Film Transistor Logic Gates**

Jianping Zou,<sup>a</sup> Kang Zhang,<sup>a</sup> Weifan Cai,<sup>a</sup> Tupei Chen,<sup>a</sup> Arokia Nathan<sup>b</sup> and Qing Zhang<sup>\*a</sup>

<sup>a</sup> Novitas, Nanoelectronics Centre of Excellence, School of Electrical & Electronic Engineering, Nanyang Technological University, 50 Nanyang Avenue, 639798, Singapore. E-mail: eqzhang@ntu.edu.sg

<sup>b</sup> Department of Engineering, Electrical Engineering Division, University of Cambridge, 9 JJ Thomson Avenue, Cambridge CB3 OFA, UK.

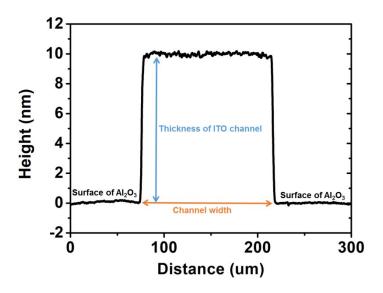

Figure S1. Thickness of the thin ITO channel layer measured using a surface profiler.

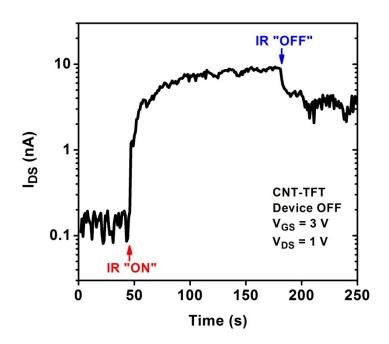

Figure S2. Photoresponse of CNT-TFT under IR (power = 2 Watt,  $\lambda$  = 1200 nm) irradiation.

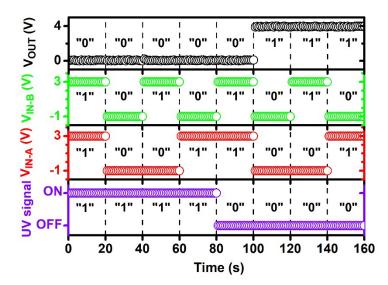

| $\mathbf{UV}_{\mathbf{IN}}$ | $V_{IN-A}$ | $V_{\text{IN-B}}$ | V <sub>OUT</sub> |

|-----------------------------|------------|-------------------|------------------|

| 0                           | 0          | 0                 | 1                |

| 0                           | 0          | 1                 | 1                |

| 0                           | 1          | 0                 | 1                |

| 0                           | 1          | 1                 | 0                |

| 1                           | 0          | 0                 | 0                |

| 1                           | 0          | 1                 | 0                |

| 1                           | 1          | 0                 | 0                |

| 1                           | 1          | 1                 | 0                |

Figure S3. Output electrical signal ( $V_{OUT}$ ) and of the NAND gate ( $V_{DD} = 4 \text{ V}$ ) under alternating UV signal (UV<sub>IN</sub>). Inset: true table of logical operation performed by UV<sub>IN</sub>,  $V_{IN-A}$ , and  $V_{IN-B}$ .

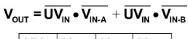

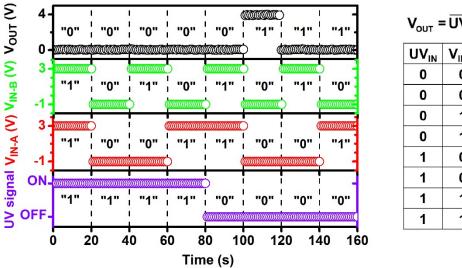

$\mathbf{V}_{\mathsf{OUT}} = \overline{\mathbf{U}\mathbf{V}_{\mathsf{IN}} + \mathbf{V}_{\mathsf{IN-A}} + \mathbf{V}_{\mathsf{IN-B}}}$  $\mathbf{V}_{\mathsf{IN-A}}$  $V_{\text{IN-B}}$ Vout

Figure S4. Output electrical signal ( $V_{OUT}$ ) and of the NOR gate ( $V_{DD} = 4$  V) under alternating UV signal (UV<sub>IN</sub>). Inset: true table of logical operation performed by UV<sub>IN</sub>,  $V_{IN-A}$ , and  $V_{IN-B}$ .