## **Electronic Supplementary Information**

## Cross-linked poly(hydroxy imide) gate-insulating materials for lowtemperature processing of organic thin-film transistors

Joo-Young Kim,<sup>ab</sup> Ji Whan Kim,<sup>a</sup> Eun Kyung Lee,<sup>a</sup> Jeong-Il Park,<sup>a</sup> Bang-Lin Lee,<sup>a</sup>

Young-Nam Kwon<sup>c</sup>, Sunjung Byun<sup>c</sup>, Myung-Sup Jung<sup>\*d</sup> and Jang-Joo Kim<sup>\*b</sup>

a. Material Research Center, SAIT, Samsung Electronics, Suwon, Gyeonggi-do 16678, Republic of Korea

b. Department of Materials Science and Engineering, Seoul National University, Seoul 08826, Republic of Korea

c. Platform Technology Lab, SAIT, Samsung Electronics, Suwon, Gyeonggi-do 16678, Republic of Korea

d. INNOX Corporation R&D Center, Asan, Chungcheongnam-do 31409, Republic of Korea

## **Corresponding Author**

\*Jang-Joo Kim (jjkim@snu.ac.kr), Myung-Sup Jung (msjung22@innoxcorp.com)

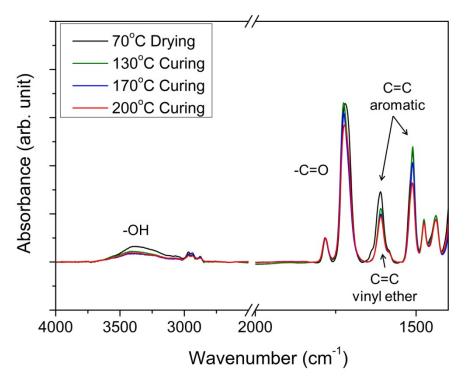

Figure S1 Comparison of FT-IR spectra of PHI 100 thin films cured at different temperatures

Table S1 The crosslinking densities estimated from the absorption reduction of the OH group

| Curing temperature | Cross-linking density |  |

|--------------------|-----------------------|--|

| 130°C              | 28 %                  |  |

| 170°C              | 31 %                  |  |

| 200°C              | 30 %                  |  |

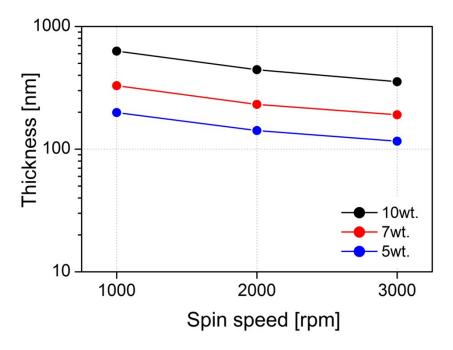

Figure S2 Thickness variation of PHI 100 thin films with tunable parameters ; solid content and spin speed

| Solid content | Spin speed | Film thickness |

|---------------|------------|----------------|

|               | [rpm]      | [nm]           |

| 10 wt.%       | 1,650      | 500            |

|               | 2,450      | 400            |

| 7 wt.%        | 1,230      | 300            |

|               | 2,700      | 200            |

| 5 wt.%        | 3,620      | 100            |

Table S2 Solid content and spin speed conditions for the deposition of PHI 100 thin films

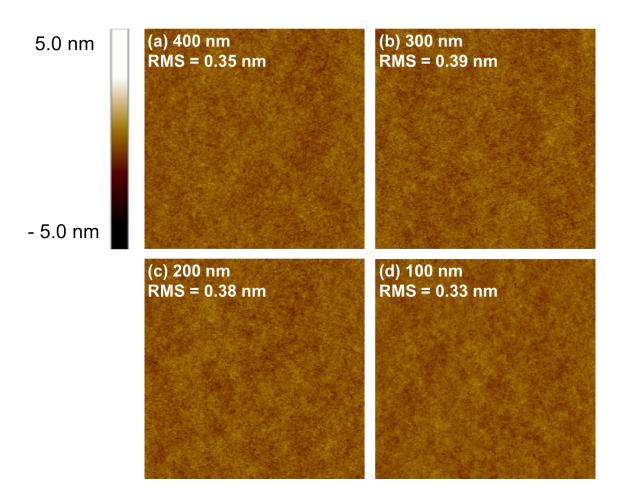

Figure S3 Surface roughness of PHI 100 thin films by AFM (5  $\mu$ m scale);

(a) 400 nm – thick film, (b) 300 nm – thick film, (c) 200 nm – thick film, (d) 100 nm – thick film

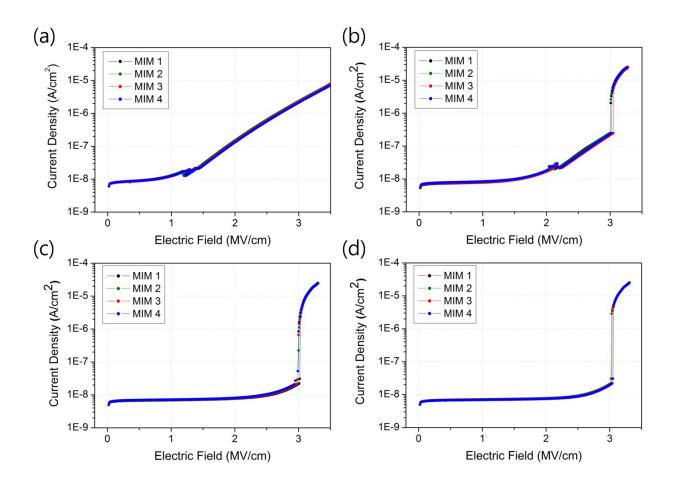

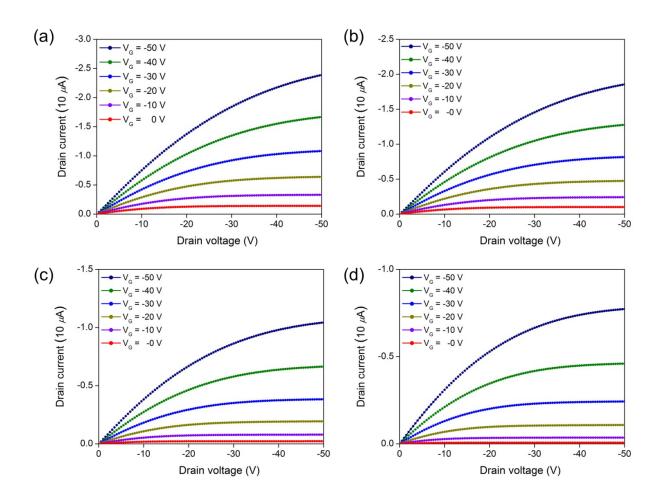

Figure S4 Leakage current densities of MIM structures fabricated from (a) PHI 0, (b) PHI 33, (c) PHI 67, (d) PHI 100

Figure S5 Output characteristics of pentacene TFTs using PHI as gate-insulating layers. (a) PHI 0 (b) PHI 33 (c) PHI 67 (d) PHI 100

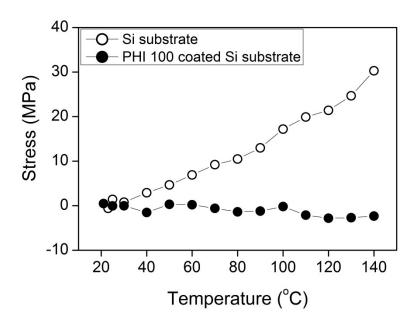

Figure S6 Stress changes with temperature for 8 inch Si substrate and 500 nm-thick PHI 100 thin film deposited on it