## Electronic Supplementary Information (ESI)

## Realization of Multi-Configurable Logic Gate Behaviour on Fluorescence Switching Signalling of Naphthalene Diimide Congeners

Hridoy Jyoti Bora,<sup>a</sup> Pranjal Barman,<sup>b</sup> Sushanta Bordoloi,<sup>c</sup> Gautomi Gogoi,<sup>a</sup> Bedanta Gogoi,<sup>d</sup> Neelotpal Sen Sarma<sup>a</sup> and Anamika Kalita<sup>a</sup>\*

- a. Physical Sciences Division, Institute of Advanced Study in Science and Technology, Paschim Boragaon, Guwahati-781035, Assam, India.

- b. Department of Electronics and Communication Technology, Gauhati University, Guwahati-781014, Assam, India.

- c. Department of Electronics and Communication Engineering, National Institute of Technology Mizoram, Aizawl-796012, India.

- d. Department of Chemistry, Gauhati University, Guwahati-781014, Assam, India.

Corresponding Author's Email: anamik.kalita01@gmail.com

## **Detailed Synthetic scheme of N2:**

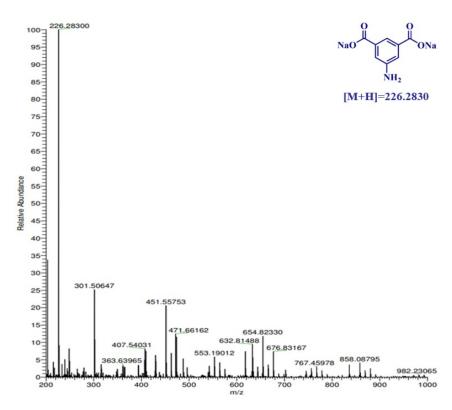

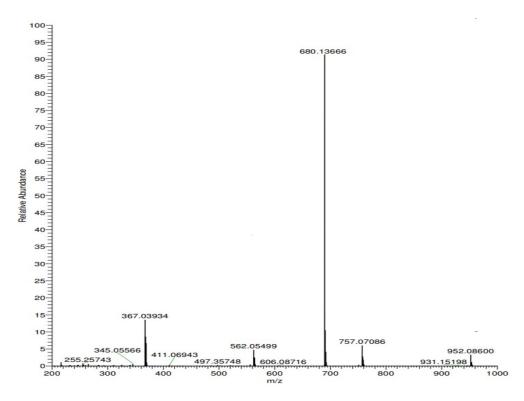

Fig. S1 ESI-MS spectra of sodium salt of 5-amino isophthalic acid.

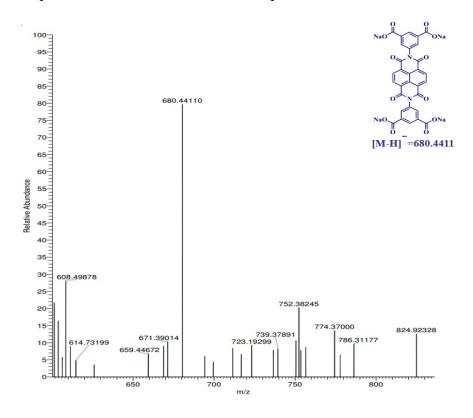

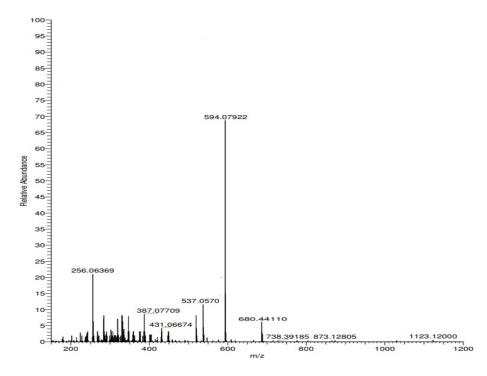

Fig. S2 ESI-MS spectra of N2.

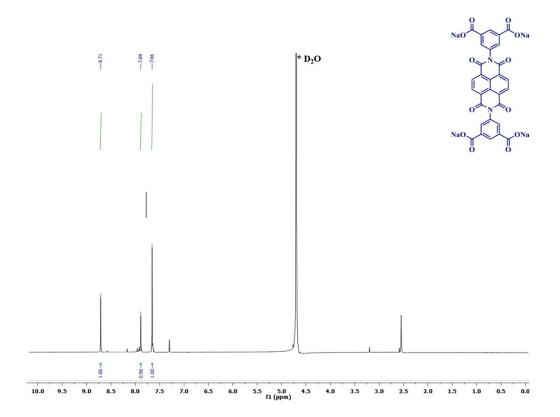

Fig. S3 <sup>1</sup>H-NMR (D<sub>2</sub>O) spectra of N2.

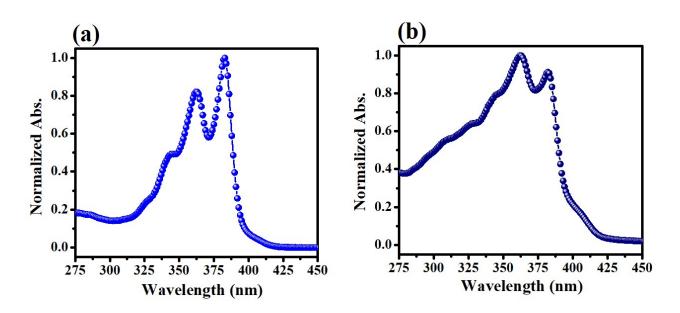

Fig. S4 Normalized absorption spectra of N1 (a) and N2 (b) in solution.

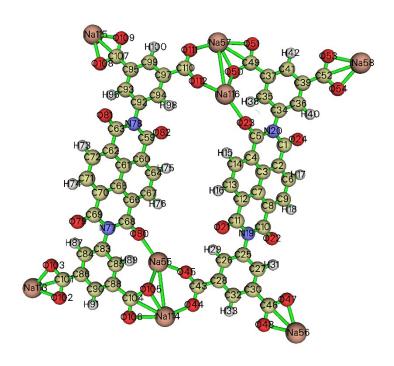

Fig. S5 Absence of Non-Covalent Interaction (NCI) in N2.

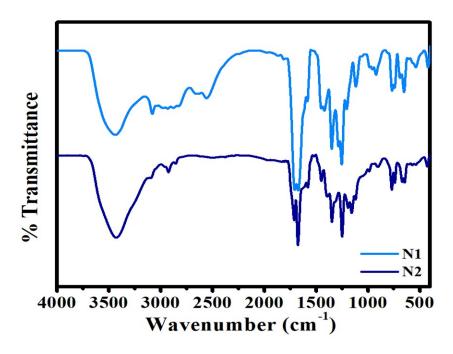

Fig. S6 FT-IR spectra of N1 and N2.

Fig. S7 ESI-MS spectra of the product formed after addition of NaOH to N1.

Fig. S8 ESI-MS spectra of the product formed after addition of HCl to N2.

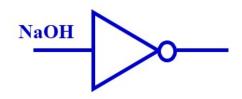

| System | Input<br>(NaOH) | Output<br>(Emission<br>intensity) |

|--------|-----------------|-----------------------------------|

| N1     | 0               | 1 (on)                            |

|        | 1               | 0 (off)                           |

Fig. S9 Representation of NOT logic gate and corresponding truth table obtained for N1.

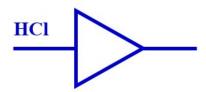

| System | Input (HCl) | Output<br>(Emission<br>intensity) |

|--------|-------------|-----------------------------------|

| N2     | 0           | 0 (off)                           |

|        | 1           | 1 (on)                            |

Fig. S10 Representation of YES logic gate and corresponding truth table obtained for N2.