## SI: Low temperature (Zn,Sn)O deposition for reducing interface open-circuit voltage deficit to achieve highly efficient Se-free Cu(In,Ga)S<sub>2</sub> solar cells

Mohit Sood\*<sup>a</sup>, Damilola Adeleye<sup>a</sup>, Sudhanshu Shukla<sup>a</sup>, Tobias Törndahl<sup>b</sup>, Adam Hultqvist<sup>b</sup>, Susanne Siebentritt<sup>a</sup> (E-mail address: <u>mohit.sood@uni.lu</u>)

<sup>a</sup>Laboratory for Photovoltaics, Department of Physics and Materials Science, University of Luxembourg, Belvaux, L-4422, Luxembourg. <sup>b</sup>Solar Cell Technology, Department of Materials Science and Engineering, Uppsala University, Uppsala, 751 21, Sweden.

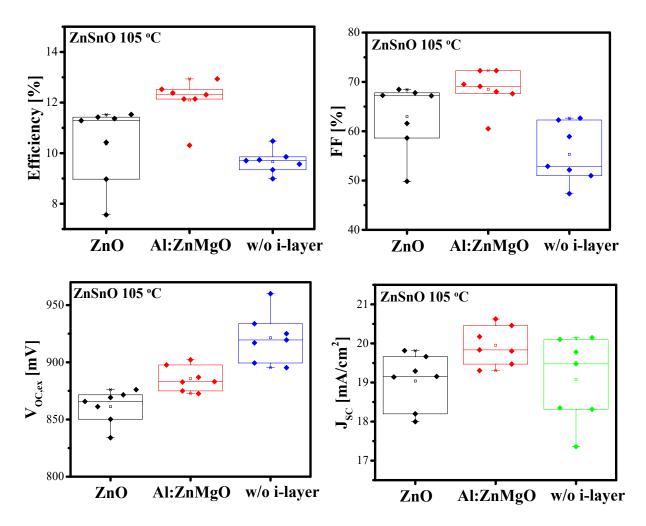

*Figure S1:* Box plot showing the distribution of J-V characteristics of Cu(In,Ga)S<sub>2</sub> devices using B1 with different i-layer combinations.

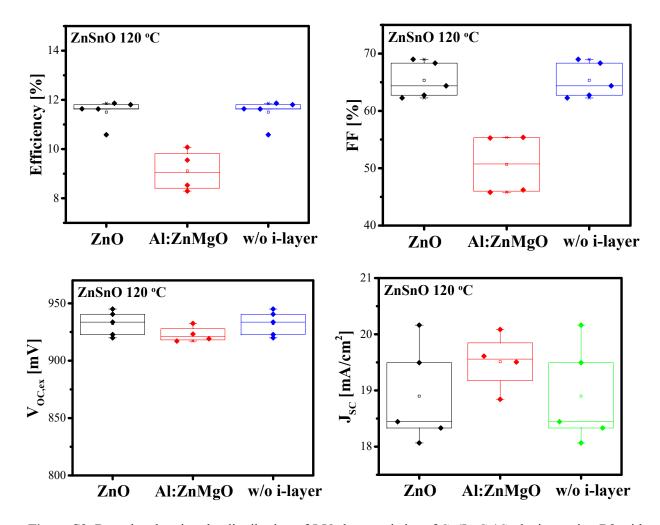

*Figure S2:* Box plot showing the distribution of J-V characteristics of Cu(In,Ga)S<sub>2</sub> devices using B2 with different i-layer combinations.

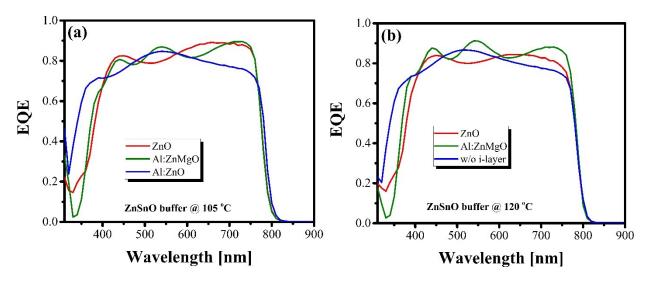

*Figure S3:* External quantum efficiency plot of (a) B1 device (b) B2 devices with different i-layer combinations.

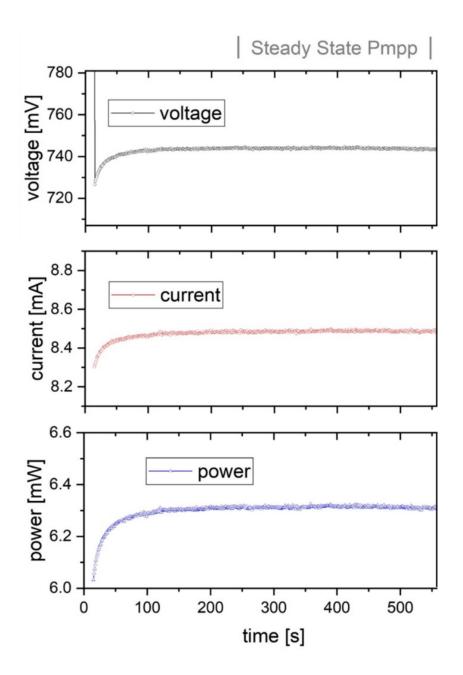

*Figure S4:* Transient curve of voltage (top), current (middle) and power (bottom) at maximum power point for the device under 100 mW/cm<sup>2</sup> illumination.

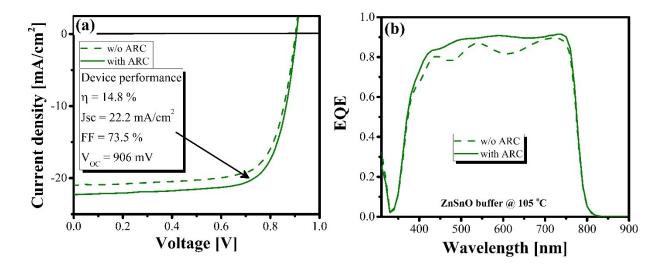

## In-house measurements of the certified device

*Figure S5:* (a) I-V curve and (b) EQE curve of the Cu(In,Ga)S<sub>2</sub> device having a PCE of 14.8 % prepared with Zn<sub>0.8</sub>Sn<sub>0.2</sub>O buffer layer deposited at 105 °C with sputtered Al:ZnMgO i-layer with and without an anti-reflective coating of MgF<sub>2</sub>.