## Boron nitride-mediated semiconductor nanonetwork for ultralow-power fibrous synaptic transistor and Creactive protein sensing

Mufang Li<sup>1†</sup>, Qing Shu<sup>1†</sup>, Xing Qing<sup>1\*</sup>, Jianmei Wu<sup>1</sup>, Qing Xiao<sup>1</sup>, Kangyu Jia<sup>1</sup>, Xungai Wang<sup>2</sup>, Dong Wang<sup>1\*</sup>

<sup>1</sup>Key Laboratory of Textile Fiber and Products (Wuhan Textile University), Ministry of Education, Wuhan Textile University, Wuhan, 430200, China

<sup>2</sup>JC STEM Lab of Sustainable Fibers and Textiles, School of Fashion and Textiles, The Hong Kong Polytechnic University, Hung Hom, Kowloon, Hong Kong, China

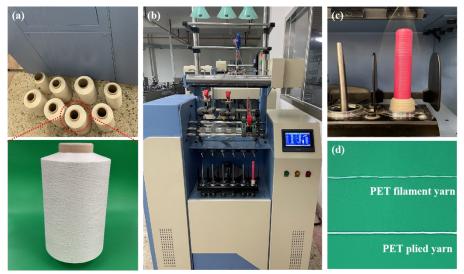

**Fig. S1.** (a)-(c) the spinning frame machine, eight commercial hydrophobic polyester (PET) filiment yarns (75D/72f) were twisting together to manufacture the PET plied yarn. (d) the photographs of PET filiments and twisted PET yarns.

<sup>&</sup>lt;sup>+</sup>These authors contributed equally.

<sup>\*</sup>Corresponding authors: (Q.X.) E-mail: <u>794315726@qq.com</u>, (D.W.) E-mail: wangdon08@126.com;

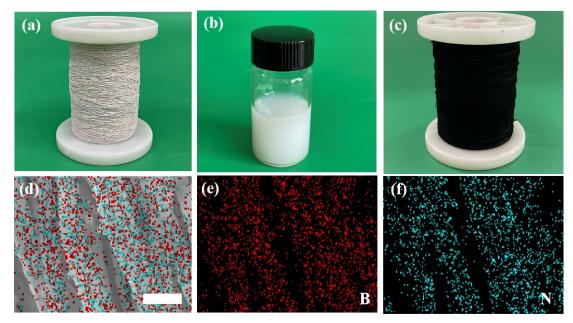

**Fig. S2.** Optical images of PET (a), FBN colloid solution (b), PPy/FBN/PET electrode (c), optical image of PPy/FBN/PET electrode, (d) the EDS images of FBN/PET electrode, (e) the B element and (f) N element.

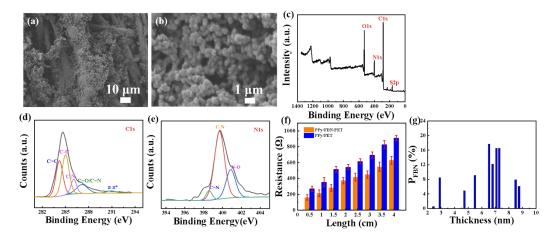

**Fig. S3.** (a)-(b) SEM images of PPy/PET, (c) XPS survey spectra of PPy/FBN/PET, (d) C1s and (e) N1s spectra.(f) the resistances of PPy/PET and PPy/FBN/PET with different measuring length. (g) FBN sheets counted from their AFM images. The average thickness of FBN is 6.05 nm.

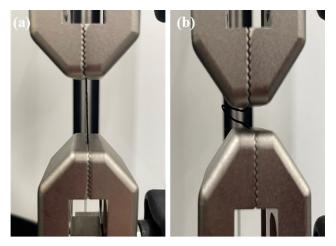

Fig. S4. The bending stability test of PPy/FBN/PET electrode by Mark 10 Force Gauges.

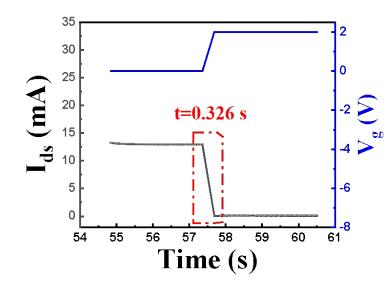

Fig. S5. The tenth switch cycle of FOECT, the response time is 0.326 s.

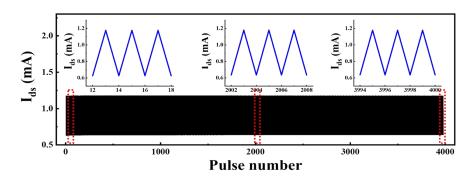

Fig. S6. EPSC stability of synaptic FOECT for 4000 cycles (Vg=1 V, 25 ms)

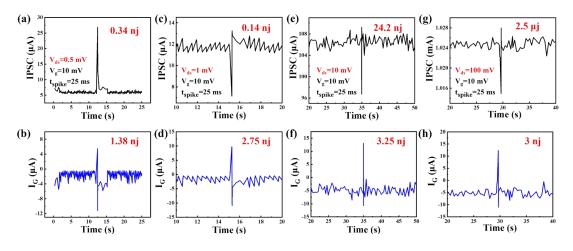

Fig. S7. Power consumption at different  $V_{ds}$  ( $V_g = 10 \text{ mV}$ , 25 ms). (a) IPSC and (b) gate power consumption at  $V_{ds} = 0.5 \text{ mV}$ . (c) IPSC and (d) gate power consumption at  $V_{ds} = 1 \text{ mV}$ . (e) IPSC and (f) gate power consumption at  $V_{ds} = 10 \text{ mV}$ . (g) IPSC and (h) gate power consumption at  $V_{ds} = 100 \text{ mV}$ .

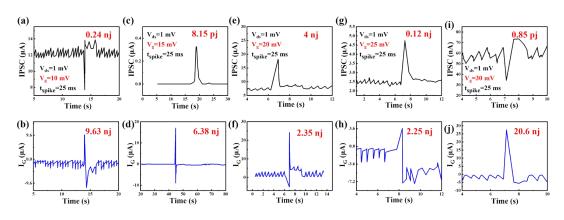

Fig. S8. Power consumption at different V<sub>g</sub> (V<sub>ds</sub> =1 mV, spike width 25 ms). (a) IPSC and (b) gate power consumption at V<sub>g</sub> =10 mV. (c) IPSC and (d) gate power consumption at V<sub>g</sub> =15 mV.

(e) IPSC and (f) gate power consumption at V<sub>g</sub> =20 mV. (g) IPSC and (h) gate power consumption at V<sub>g</sub> =25 mV. (i) IPSC and (j) gate power consumption at V<sub>g</sub> =30 mV.