Electronic Supplementary Material (ESI) for Journal of Materials Chemistry C. This journal is © The Royal Society of Chemistry 2024

## **Electronic Supplementary Material**

## Low-Voltage Polymer Monolayer Transistors for High-Gain Unipolar and Complementary Logic Inverters

Miao Cheng<sup>a,b†</sup>, Yanqin Zhang<sup>a†</sup>, Lei Zheng<sup>a†</sup>, Jianwei Zhang<sup>c</sup>, Yifan Xie<sup>a</sup>, Qingqing Jin<sup>a</sup>, Yue Tian<sup>a</sup>, Jinyao Wang<sup>a</sup>, Hongmei Xiao<sup>d</sup>, Chunmeng Dou<sup>a</sup>, Zhenzhong Yang<sup>c</sup>, Mengmeng Li<sup>a,b\*</sup>, Ling Li<sup>a</sup>, Ming Liu<sup>a</sup>

<sup>&</sup>lt;sup>a</sup>-Key Lab of Fabrication Technologies for Integrated Circuits, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China.

<sup>&</sup>lt;sup>b.</sup>University of Chinese Academy of Sciences, 100049 Beijing, China.

<sup>&</sup>lt;sup>c.</sup>Key Laboratory of Polar Materials and Devices (MOE) and Department of Electronics, East China Normal University, 200241 Shanghai, China.

<sup>&</sup>lt;sup>d</sup>·Key Laboratory of Science and Technology on Space Energy Conversion, Technical Institute of Physics and Chemistry, Chinese Academy of Sciences, Beijing 100190, China

<sup>&</sup>lt;sup>†</sup>Contributed equally to this work.

<sup>\*</sup>Email: limengmeng@ime.ac.cn

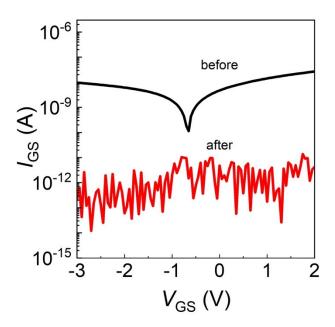

**Figure S1** The gate leakage currents ( $I_{GS}$ ) of polymer monolayer TFTs before and after patterning using the sacrificial layer strategy.

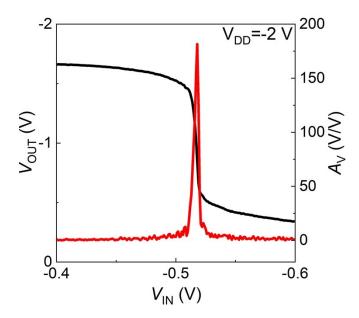

**Figure S2** Input-output characteristics and voltage gain of zero- $V_{\rm GS}$ -load inverter based on polymer monolayer TFTs at  $V_{\rm DD}$  = -2 V.

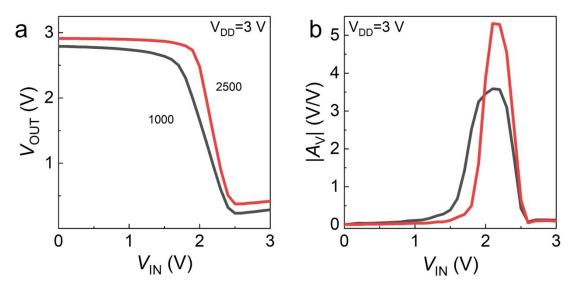

**Figure S3** Influence of channel width of driver transistor on the performance of diode-load inverters. The channel width of driver transistor is 1000 and 2500  $\mu$ m in this figure and 5000  $\mu$ m in Fig. 4b.

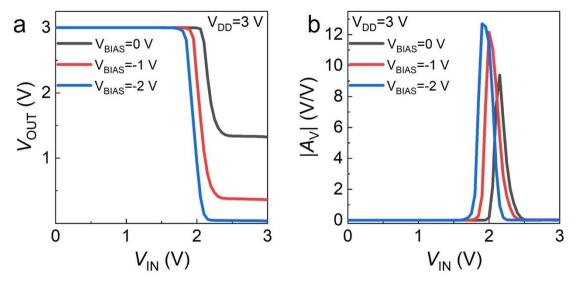

**Figure S4** Influence of channel width of bias voltage ( $V_{BIAS}$ ) on the performance of pseudo-E inverters. The bias voltage is -1 and -2 V in this figure and -3 V in Fig. 4e.

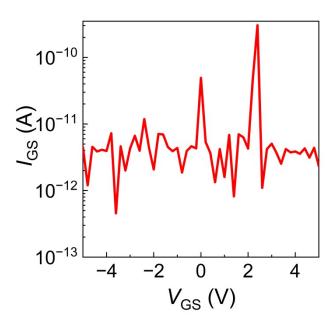

Figure S5 The gate leakage currents (IGS) of IGZO TFTs after patterning

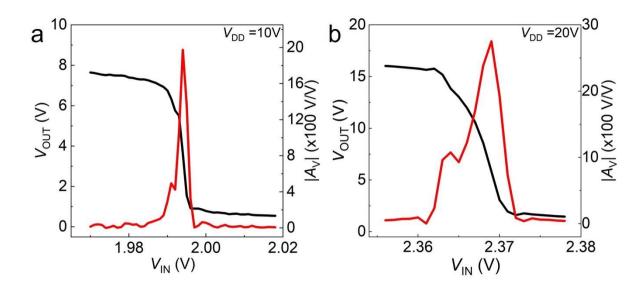

Figure S6 Input-output characteristics of complementary inverter at various  $V_{\rm DD}$ .

**Table S1** Channel dimension of TFTs reported in this work.

| channel dimension     |            | channel length (μm) | channel width (μm) | number of TFTs |

|-----------------------|------------|---------------------|--------------------|----------------|

| polymer monolayer TFT |            | 20                  | 1000               | -              |

| IGZO TFT              |            | 10                  | 20                 | -              |

| zero- $V_{GS}$ -load  | driver TFT | 5                   | 90                 | 2              |

| inverter              | load TFT   | 5                   | 180                | 2              |

| diode-load inverter   | driver TFT | 5                   | 5000               | 2              |

|                       | load TFT   | 5                   | 20                 |                |

| Pseudo-E inverter     | driver TFT | 5                   | 5000               | 4              |

|                       | load TFT   | 5                   | 20                 |                |