Supplementary Information (SI) for Energy & Environmental Science. This journal is © The Royal Society of Chemistry 2025

#### Supplementary Information

# A Universal Self-Triggered Passive Management Strategy for Output Power of Triboelectric Nanogenerator

Zhenjie Wang<sup>1,2,4</sup>, Jianlong Wang<sup>1,4</sup>, Zheng Yang<sup>1,4</sup>, Jinzhi Zhu<sup>1</sup>, Peinian Zhang<sup>1</sup>, Xin Yu<sup>1</sup>, Hengyu Li<sup>1</sup>, Yang Yu<sup>1\*</sup>, Yu Zhang<sup>2\*</sup>, Zhong Lin Wang<sup>1,3\*</sup>, Tinghai Cheng<sup>1,3\*</sup>

<sup>1</sup> Beijing Institute of Nanoenergy and Nanosystems, Chinese Academy of Sciences, Beijing 101400, China

<sup>2</sup> State Key Laboratory of Integrated Optoelectronics, JLU Region, Changchun 130012, China

<sup>3</sup> Guangzhou Institute of Blue Energy, Guangzhou 510555, China

<sup>4</sup> These authors contributed equally: Zhenjie Wang, Jianlong Wang, Zheng Yang.

\*Corresponding authors' e-mail addresses:

Yang Yu: yuyang@binn.cas.cn;

Yu Zhang: yuzhang@jlu.edu.cn;

Zhong Lin Wang: zhong.wang@mse.gatech.edu;

Tinghai Cheng: chengtinghai@binn.cas.cn

#### **Content**

#### **Supplementary Figures:**

Supplementary Fig. 1. Schematic diagram of the buck circuit operation.

**Supplementary Fig. 2.** Schematic diagram of the hysteresis comparator circuit operation.

Supplementary Fig. 3. Simulation of the simulated TENG signal.

Supplementary Fig. 4. The input capacitor voltage signal is simulated and tested.

**Supplementary Fig. 5.** Voltage variations across the output capacitor caused by changes in input capacitance and inductance in the simulated buck circuit.

**Supplementary Fig. 6.** Timing diagram of the overall system in the simulation test.

**Supplementary Fig. 7.** Power consumption of each resistor in the hysteresis circuit when a 1K load is connected in the simulation test.

**Supplementary Fig. 8.** Performance testing of the TENG in vertical contact-separation mode at different frequencies.

**Supplementary Fig. 9.** Output current variation of the freestanding mode TENG after connecting to the buck circuit.

**Supplementary Fig. 10.** Comparison of charging times for different output capacitors in vertical contact-separation mode testing.

**Supplementary Fig. 11.** Influence of different inductances on the charging time of the output capacitor in vertical contact-separation mode testing.

**Supplementary Fig. 12.** Hysteresis module testing.

**Supplementary Fig. 13.** TENG directly powering the load after rectification.

**Supplementary Fig. 14.** TENG directly powering the load after rectification and buck circuit.

**Supplementary Fig. 15.** Output voltage variation with different output capacitors when the system is connected to different purely resistive loads.

**Supplementary Fig. 16.** System waveform variation in actual testing.

**Supplementary Fig. 17.** Voltage variation when the system is connected to different purely resistive loads (hysteresis turn-on voltage set to 3V).

**Supplementary Fig. 18.** Output power and duration variation with different loads.

Supplementary Fig. 19. TENG load power test.

**Supplementary Fig. 20.** Load power in the hysteresis working phase after integrating TENG with PMS.

**Supplementary Fig. 21.** Humidity and temperature meter photograph and performance test.

Supplementary Fig. 22. Wireless sensor module photograph.

Supplementary Fig. 23. Photographs of passive components used.

Supplementary Fig. 24. Application test host computer display interface.

# **Supplementary Notes:**

**Supplementary Note 1.** Buck circuit workflow and principal analysis.

Supplementary Note 2. Hysteresis circuit workflow and principal analysis.

**Supplementary Note 3.** System simulation test.

Supplementary Note 4. Component selection explanation.

Supplementary Note 5. Layout of circuit.

Supplementary Note 6. Formula calculation.

#### **Supplementary Tables:**

Supplementary Table 1. Abbreviations and meanings appearing in the paper.

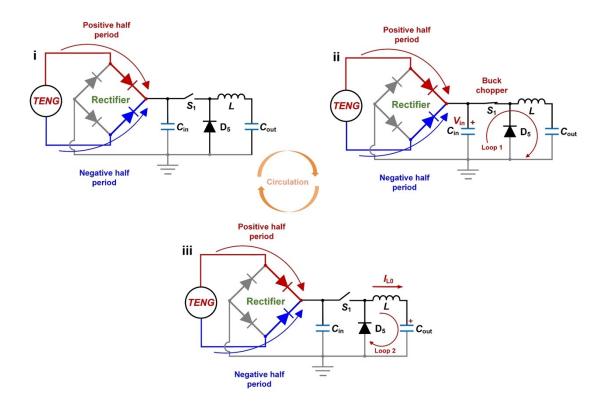

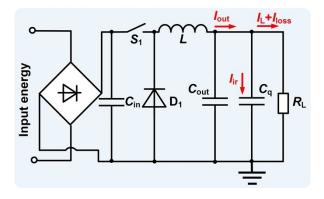

Supplementary Fig. 1. Schematic diagram of the buck circuit operation.

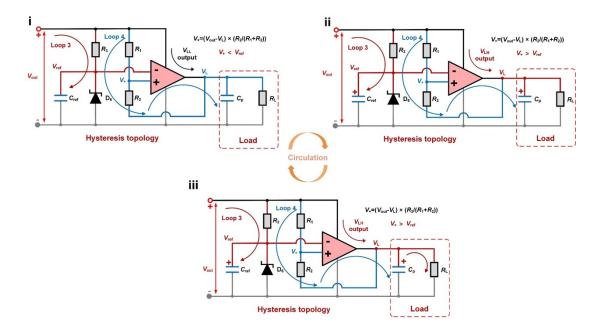

**Supplementary Fig. 2.** Schematic diagram of the hysteresis comparator circuit operation.

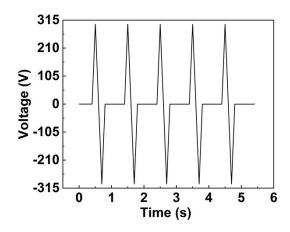

Supplementary Fig. 3. Simulation of the simulated TENG signal.

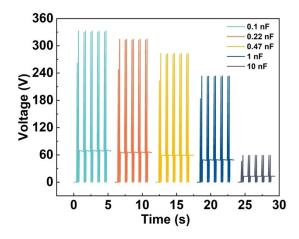

Supplementary Fig. 4. The input capacitor voltage signal is simulated and tested.

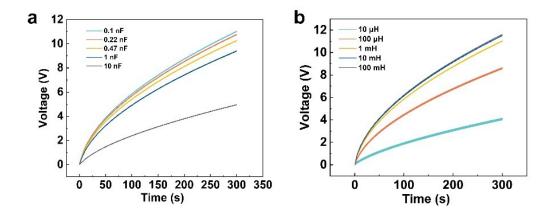

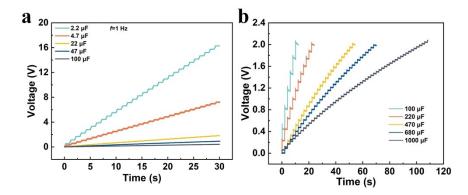

**Supplementary Fig. 5.** Voltage variations across the output capacitor caused by changes in input capacitance and inductance in the simulated buck circuit. **a** Output capacitor charging test with varying input capacitance. **b** Output capacitor charging test with varying inductance.

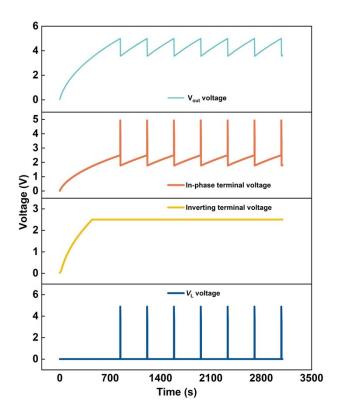

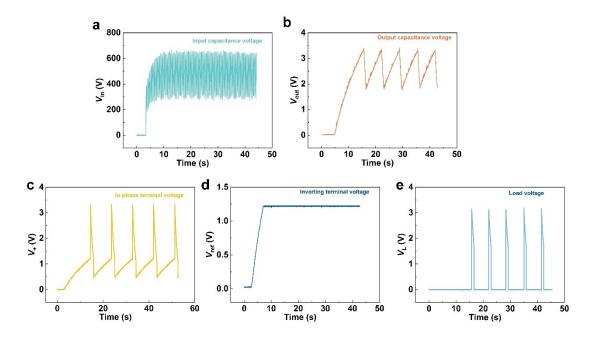

Supplementary Fig. 6. Timing diagram of the overall system in the simulation test.

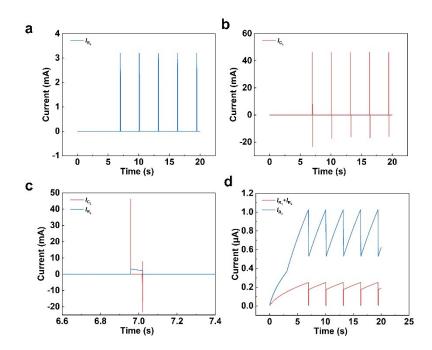

**Supplementary Fig. 7.** Power consumption of each resistor in the hysteresis circuit when a 1K load is connected in the simulation test. **a** Power consumption of the load. **b** Power consumption across the load capacitor. **c** Current through the load and load capacitor. **d** Current consumption of resistors in the hysteresis module.

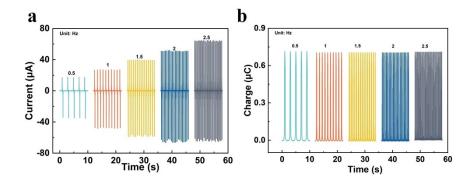

**Supplementary Fig. 8.** Performance testing of the TENG in vertical contact-separation mode at different frequencies. **a** Short-circuit current test. **b** Transferred charge test.

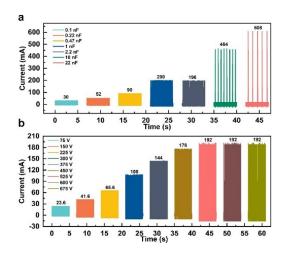

**Supplementary Fig. 9.** Output current variation of the freestanding mode TENG after connecting to the buck circuit. **a** Current variation with different input capacitors. **b** Current variation under different breakdown voltages.

**Supplementary Fig. 10.** Comparison of charging times for different output capacitors in vertical contact-separation mode testing. **a** Voltage variation without the buck circuit. **b** Voltage variation with the buck circuit.

**Supplementary Fig. 11.** Influence of different inductances on the charging time of the output capacitor in vertical contact-separation mode testing.

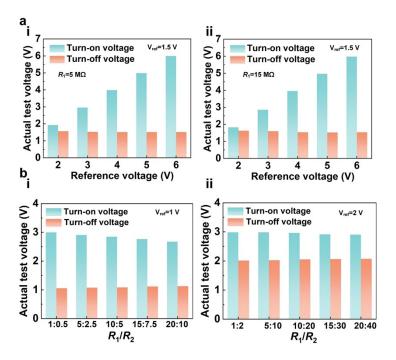

**Supplementary Fig. 12.** Hysteresis module testing. **a** Variation between the actual measured values and set values at different set voltages. (i)  $R_1$ = 5 M $\Omega$ , (ii)  $R_1$ =15 M $\Omega$ . **b** Effect of different voltage divider resistor ratios on actual values with different reference voltages. (i) 1V reference voltage, (ii) 2V reference voltage.

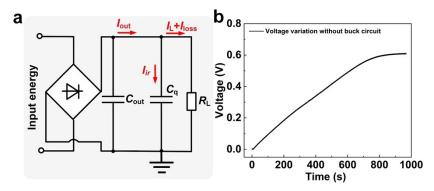

**Supplementary Fig. 13.** TENG directly powering the load after rectification. **a** Circuit diagram. **b** Output voltage waveform.

**Supplementary Fig. 14.** TENG directly powering the load after rectification and buck circuit.

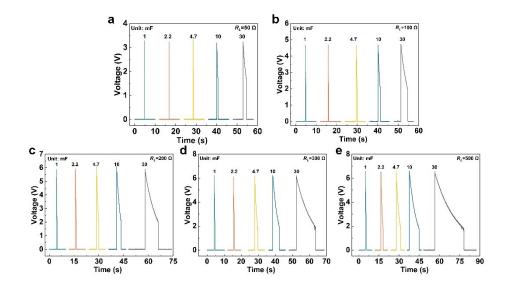

Supplementary Fig. 15. Output voltage variation with different output capacitors when the system is connected to different purely resistive loads. **a** 50  $\Omega$ . **b** 100  $\Omega$ . **c** 200  $\Omega$ . **d** 300  $\Omega$ . **e** 500  $\Omega$ .

Supplementary Fig. 16. System waveform variation in actual testing. a Voltage across the input capacitor. b Voltage across the output capacitor. c Voltage at the non-inverting terminal. d Voltage at the inverting terminal. e Voltage across the load.

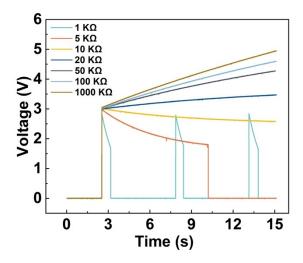

**Supplementary Fig. 17.** Voltage variation when the system is connected to different purely resistive loads (hysteresis turn-on voltage set to 3V).

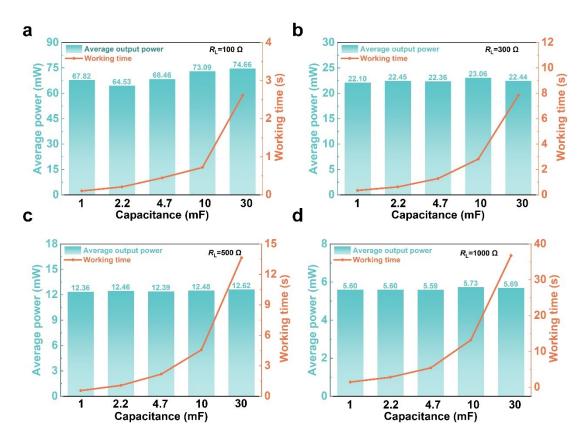

**Supplementary Fig. 18.** Output power and duration variation with different loads. **a**  $100 \Omega$ . **b**  $300 \Omega$ . **c**  $500 \Omega$ . **d**  $1000 \Omega$ .

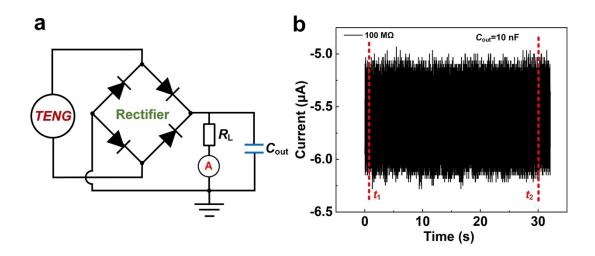

Supplementary Fig. 19. TENG load power test. a Test circuit diagram. b Output current with  $100~\text{M}\Omega$  load.

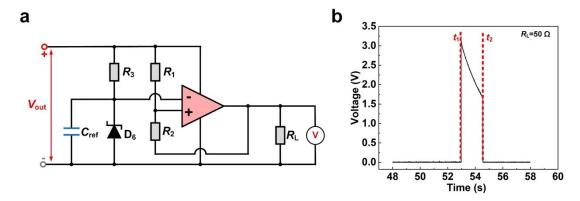

Supplementary Fig. 20. Load power in the hysteresis working phase after integrating TENG with PMS. a Schematic of the experimental circuit. b Output voltage across a  $50 \Omega$  load.

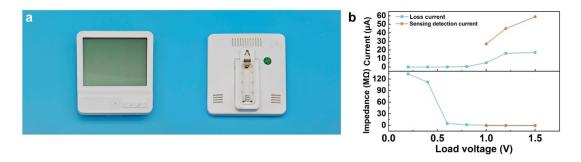

**Supplementary Fig. 21.** Humidity and temperature meter photograph and performance test. **a** Physical photo of the meter. **b** Loss current and equivalent impedance at different voltages.

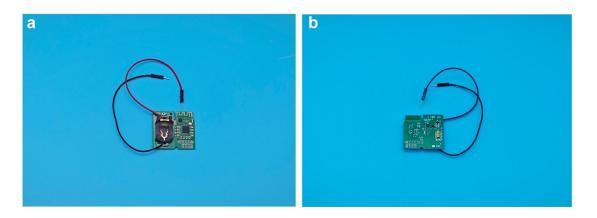

Supplementary Fig. 22. Wireless sensor module photograph. a Front view. b Back view.

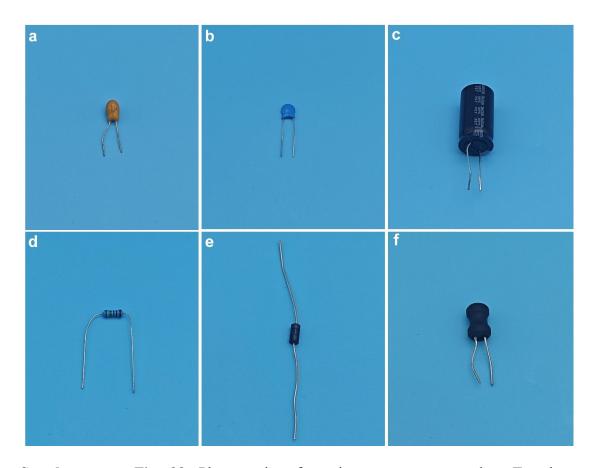

**Supplementary Fig. 23.** Photographs of passive components used. **a** Tantalum capacitor. **b** Ceramic capacitor. **c** Electrolytic capacitor. **d** Metal film resistor. **e** Diode. **f** Drum core inductor.

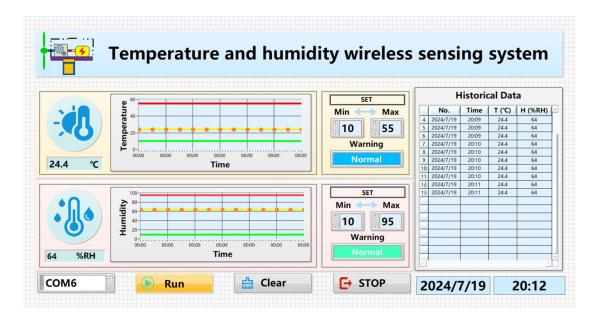

Supplementary Fig. 24. Application test host computer display interface.

## Supplementary Note 1. Buck circuit workflow and principal analysis.

Figure S1 shows the basic working principle of the Buck module in the system. As the electrodes in the Triboelectric Nanogenerator move back and forth, they generate an AC signal. This AC signal is rectified into DC by a rectifier circuit, and the energy is stored in the input capacitor  $C_{\rm in}$ , as shown in Figure S1(i). The design allows the TENG output to be processed smoothly and efficiently, providing a stable energy supply to the subsequent circuits.

The switching mechanism  $S_1$  uses a silicon controlled rectifier (SCR) and a zener diode connected in reverse parallel. When  $V_{\rm in}$  rises to the Zener diode's breakdown voltage, the diode breaks down, triggering the SCR to turn on, and allowing the charge stored in  $C_{\rm in}$  to transfer to the rear inductor, as shown in Figure S1(ii). Input capacitance  $C_{\rm in}$ , the switching device, inductor L, and output capacitor  $C_{\rm out}$  form a circuit loop. The SCR is a semi-controlled device, and when the current drops below the holding current, the SCR turns off. At that point, L,  $C_{\rm out}$ , and the freewheeling diode  $D_5$  form a loop. In order to maintain the current direction, L generates a back electromotive force, and the stored energy is transferred to  $C_{\rm out}$ , as shown in Figure S1(iii). This process converts the high-voltage, low-current signal from the TENG into a low-voltage, high-current output, which is better suited for powering downstream circuits or loads.

## Supplementary Note 2. Hysteresis circuit workflow and principal analysis.

Figure S2 illustrates the basic working principle of the hysteresis module. The hysteresis circuit is connected in parallel with  $C_{\rm out}$ , and  $V_{\rm out}$  serves as the input voltage for the hysteresis module. The input side forms a loop with  $R_3$ , the reference capacitor  $C_{\rm ref}$ , and the voltage divider reference source  $D_6$ .  $R_1$ ,  $R_2$ , and the load form another loop.  $C_{\rm ref}$  provides a reference voltage  $V_{\rm ref}$  to the inverting terminal of the comparator, while  $V_{\rm out}$  is divided by  $R_1$  and  $R_2$  to provide the non-inverting terminal voltage  $V_+$ . When  $V_+$  is lower than  $V_{\rm ref}$ , the comparator outputs a low-level signal  $V_{\rm LL}$ , as shown in Figure S2 (i). When  $V_+$  exceeds  $V_{\rm ref}$ , the comparator outputs a high-level signal  $V_{\rm LH}$ , as shown in Figure S2 (ii). For the load model used in this study, the system first charges the capacitor  $C_p$  to the input voltage, and then both the capacitor and the input power supply the load, as shown in Figure S2 (iii).

In hysteresis circuit, the front-end buck circuit transfers the input energy from the TENG to the  $C_{\rm out}$ . When the energy in the storage capacitor accumulates to a certain level and the voltage reaches the load's operating voltage, the comparator outputs a high level and powers the load. Notably, during the power supply process, both the energy storage capacitor and the TENG contribute to the output power, rather than relying entirely on the real-time output of the TENG, which effectively enhances the system's average output power.

#### Supplementary Note 3. System simulation test.

Figure S3 illustrates the input parameters set for the source during the system simulation test, which are referenced based on the output characteristics of the TENG. The TENG model utilizes an existing voltage source series capacitor model to simulate its real-world behavior. Specifically, the voltage signal is set as an AC signal with a peak-to-peak value of 600 V, an inherent capacitance of 2 nF, and a signal frequency of 1 Hz. These parameters are designed to accurately reflect the operating characteristics of the TENG, ensuring the reliability of the simulation results.

The simulation primarily focuses on analyzing and validating the performance of the Buck circuit and the hysteresis comparator circuit. Figure S4 shows the voltage variation during the buck conversion process with different  $C_{\rm in}$ . The input capacitor values tested are 0.1 nF, 0.22 nF, 0.47 nF, 1 nF, and 10 nF, selected to analyze the effect of capacitance on voltage regulation. The results indicate that the choice of different capacitor values significantly impacts the stability of the output voltage and the charging speed.

Figure S5 further details the impact of capacitance and inductance on the output voltage during the simulation. Figure S5(a) shows the charging voltage variation over the same time period for an  $C_{\rm out}$  of 1 mF under different  $C_{\rm in}$ . Figure S5(b) illustrates the charging voltage of  $C_{\rm out}$  (still 1 mF) under varying inductance values during the same charging time. Through the buck conversion, the TENG signal is converted from high voltage and low current to low voltage and high current, which significantly improves the system's energy transfer efficiency.

The timing diagram of the hysteresis comparator module is shown in Figure S6. In this part of the simulation, 10 mF output capacitor  $C_{\rm out}$  is selected to effectively power the subsequent circuits. The hysteresis circuit's turn-on voltage is set to 5 V, with a reference voltage  $V_{\rm ref}$  of 2.5 V. During the operation of the buck module, energy is transferred from  $C_{\rm in}$  to  $C_{\rm out}$ , causing the voltage  $V_{\rm out}$  across  $C_{\rm out}$  to gradually increase over time. Due to the influence of the voltage divider resistors, the voltage at the non-inverting terminal  $V_+$  remains lower than  $V_{\rm ref}$  during the charging process. As  $V_{\rm ref}$  rises with the increase in  $V_{\rm out}$ , it stabilizes once it reaches the set reference voltage of 2.5 V.

To verify the system's load response, a 1 K resistor and a 47  $\mu$ F capacitor in parallel were used as a simulated load. The power loss caused by resistors in the hysteresis circuit and the current variation at the load are shown in Figure S7. Figure S7(a) displays the current flowing through the resistive load, while Figure S7(b) shows the significant surge current generated by the capacitive load at the initial power-up. To better illustrate the difference between the two, Figure S7(c) presents the magnified waveforms of both currents. Figure S7(d) shows the current loss through resistors  $R_1$ ,  $R_2$ , and  $R_3$ , further verifying the energy management performance of the circuit design.

Supplementary Note 4. Component Selection Explanation.

Figure S23 illustrates the passive components used in the circuit: (a) tantalum capacitor, (b) ceramic capacitor, (c) aluminum electrolytic capacitor, (d) metal film resistor, (e) freewheeling diode, and (f) drum core inductor.

In the Universal Self-Triggered Passive Output Power Management Strategy (USPT-PMS), the input capacitor Cin is a ceramic capacitor. Since the signal from the TENG after the rectifier is a high-voltage signal, and to match the inherent capacitance of the TENG, a small-capacity, high-voltage ceramic capacitor is chosen. According to the derating guidelines, the ceramic capacitor should have a voltage rating of at least 2 kV to ensure safety and stability.

Tantalum capacitors are used in USTP-PMS due to their low equivalent series resistance (ESR), high stability, and excellent frequency characteristics, making them ideal for filtering applications. Therefore, a tantalum capacitor is selected for  $C_{\rm ref}$ , with a common voltage rating of 16 V. The value of  $C_{\rm ref}$  is selected based on the following considerations: since  $R_3$  and  $C_{\rm ref}$  form a series circuit, the voltage on  $V_{\rm ref}$  is affected by the time constant  $\tau$ . Therefore,  $C_{\rm ref}$  should not be too large, while still providing sufficient filtering to ensure stable  $V_{\rm ref}$  output. The capacitance value is selected to be 1  $\mu$ F.

To store more energy for powering the rear-end load, the output capacitor  $C_{\rm out}$  requires a high capacitance value. Aluminum electrolytic capacitors are an effective choice for large capacitance. Since the supply voltage to the load is relatively low, a 16 V-rated electrolytic capacitor is chosen for  $C_{\rm out}$ .

Metal film resistors are commonly used in circuit designs related to triboelectricity. Resistors with at least M $\Omega$ -level resistance should be selected to minimize potential current losses. However, special attention must be paid when designing  $R_3$ ; while a higher  $R_3$  can reduce current loss, it can also increase the rise time of  $V_{\text{ref}}$ , affecting system responsiveness. Similarly, excessively high  $R_1$  and  $R_2$  values can impact the turn-on voltage of the hysteresis module.

Comparator Selection: A low-power comparator is required to minimize the impact on input energy. In this study, the comparator used is the MCP6541, with a maximum quiescent current of  $1\mu A$ . Other low-power comparators can also be used in USPT-PMS, such as the LTC1540 (quiescent current of 300 nA) and the TLV3491 (quiescent current of  $1.2 \mu A$ ).

Similarly, the reference voltage source must offer precision while maintaining low power consumption. The reference voltage source used in this study is the MAX6006, which provides a 1.25 V reference voltage (this reference is particularly suitable for applications with space constraints and low power requirements, with a minimum operating current of less than 1  $\mu$ A). For higher reference voltages, MAX6007, MAX6008, and MAX6009 can be used, offering outputs of 2.048 V, 2.5 V, and 3 V, respectively. Some comparators, like the LTC1540, have built-in reference sources and can directly provide the reference voltage. Additionally, external power sources can also serve as reference sources, and due to the very high input impedance of the inverting terminal of the comparator (up to  $T\Omega$ ), the resulting power loss is negligible.

## Supplementary Note 5. Layout of circuit.

In the circuit layout of USTP-PMS, attention should be paid to the accuracy of analog circuits. In order to reduce the noise interference of the input power supply and ensure that the comparator can work stably and reliably, a ceramic capacitor is added to the power pin of the comparator (between the power supply terminal and the ground) for filtering, which is used to filter out high-frequency noise and prevent the fluctuation of the front-end input voltage from interfering with the comparator, thereby avoiding the occurrence of false triggering of the comparator judgment.

In addition to adding filter capacitors to the power pins, ceramic capacitors are also added on the load side. This capacitor is mainly used to further reduce power supply noise and ground bounce (ground voltage changes caused by power supply current fluctuations).

In addition to selecting appropriate filter capacitors, the lead lengths of the input and output terminals should be shortened as much as possible. Long leads will introduce additional parasitic inductance and capacitance, which may cause unnecessary parasitic feedback around the comparator and interfere with the normal operation of the comparator.

#### Supplementary Note 6. Formula calculation.

#### **Buck module**

The current through the inductor at the instant the switch is turned on is equal to the sum of the output current  $i_L$  from the TENG source  $i_o$  and the current  $i_{in}$  through the input capacitor  $C_{in}$ .

$$i_{\rm r}(t) = i_{\rm in}(t) + i_{\rm o}(t)$$

(1)

Voltage across the inductor:

$$V_{\rm L}(t) = L \frac{\mathrm{d}i_{\rm L}(t)}{dt} = V_{\rm in}(t) - V_{\rm out}(t) \tag{2}$$

Current through the inductor:

$$i_{\rm L}(t) = \frac{C_{\rm o}C_{\rm in}}{C_{\rm o} + C_{\rm in}} \frac{{\rm d}V_{\rm in}(t)}{{\rm d}t}$$

(3)

When the switch is off, neglecting the diode forward voltage drop, the relationship between the inductor current and the output voltage is as follows:

$$i_{\rm L}(t) = -i_{\rm out}(t) + i_{\rm R}(t) \tag{4}$$

$$V_{\rm L}(t) = L \frac{\mathrm{d}i_{\rm L}(t)}{\mathrm{d}t} = -V_{\rm out}(t) \tag{5}$$

# Hysteresis module

$i_R$  is the total current flowing into the subsequent hysteresis circuit.

The output voltage of the hysteresis module is as follows. which includes:

$$i_R(t) = i_{R_3}(t) + i_{R_1 + R_2}(t) + i_c(t)$$

(6)

Among them,  $i_{R_3}$  is the current in the voltage divider reference source branch,  $i_{R_1+R_2}$  is

the current in the voltage divider resistor branch, and  $i_c$  is the input current of the comparator. When the voltage does not reach the limit set by the voltage divider reference source, the reference voltage  $V_{ref}$  is:

$$V_{\text{ref}}(t) = V_{\text{out}}(t) - i_{R_2}(t)R_3$$

(7)

When  $V_{\text{ref}}$  reaches its maximum value, the voltage across  $R_3$  both ends are as follows:

$$V_{R_{o}}(t) = V_{\text{out}}(t) - V_{\text{ref}}(t)$$

(8)

Non-inverting input voltage  $V_+$ :

$$V_{+}(t) = [V_{\text{out}}(t) - V_{\text{L}}(t)] \times \frac{R_{2}}{R_{1} + R_{2}}$$

(9)

Among them,  $V_L$  is the voltage across the load.

When condition  $V_+ < V_{\text{ref}}$  is met, the comparator outputs low level signal, denoted as  $V_{\text{LL}}$ .

$$V_{\rm L}(t) = V_{\rm LL}(t) \tag{10}$$

When condition  $V_+ > V_{\text{ref}}$  is met, the comparator outputs high level signal, denoted as  $V_{\text{LH}}$ .

$$V_{\rm L}(t) = V_{\rm LH}(t) \tag{11}$$

#### Performance calculation

The output power calculation of the TENG is shown in Figure S19. After passing through the rectifier bridge, the current flowing through the load is measured, with the average current  $I_{rms}$ :

$$I_{\text{rms}}(t) = \sqrt{\frac{\int_{t_1}^{t_2} I^2 d(t)}{t_2 - t_1}}$$

(12)

Average power  $P_{\rm rms}$ :

$$P_{\text{rms}}(t) = I_{\text{rms}}^{2}(t) \times R = \frac{R \times \int_{t_{1}}^{t_{2}} I^{2} d(t)}{t_{2} - t_{1}}$$

(13)

The output power calculation of the TENG connected to the PMS is shown in Figure S20. Figure S20(a) presents the test circuit diagram, which omits the front-end buck circuit section following the rectification of the TENG. Considering the range limitations of the 6514 Electrometer, as shown in Figure S20 (b), the average voltage  $V_{\rm rms}$  across the resistive load is:

$$V_{\text{rms}}(t) = \sqrt{\frac{\int_{t_1'}^{t_2'} V^2 d(t)}{t_2' - t_1'}}$$

(14)

Average power  $P'_{rms}$ :

$$P'_{\text{rms}}(t) = \frac{V_{\text{rms}}^{2}(t)}{R} = \frac{\int_{t_{1}'}^{t_{2}'} V^{2} d(t)}{(t_{2}' - t_{1}') \times R}$$

(15)

#### Load end loss calculation

The test load is a commercial wireless temperature and humidity sensor, with the specific physical image shown in Supplementary Fig. 22. Without using the hysteresis module, the buck circuit is employed for voltage step-down and current boosting. After connecting the load, as shown in Fig. 4b (ii) and (iii), the load current gradually stabilizes after 13 s. At this point, the voltage across the load  $V_L$  equals the voltage across the output capacitor  $V_{\text{out}}$ .

$$V_{\rm L}(t) = V_{\rm out}(t) \tag{16}$$

$V_L$ =1.3 V, the current flowing through the load is  $I_L$ , Since the operating voltage of the load has not been reached, the current flowing through the load at this time can be considered as a loss current  $I_{loss}$ ,

$$I_{\rm L}(t) = I_{\rm loss}(t) \tag{17}$$

$I_{\rm loss}$ =3.8 mA, the loss is represented as  $P_{\rm loss}$ :

$$P_{loss}(t) = V_{L}(t) \times I_{loss}(t) = 4.94 \text{ mW}$$

(18)

Since the output signal gradually increases and fluctuates, the calculated loss represents the maximum loss.

After connecting the USTP-PMS, the comparator outputs a low-level voltage  $V'_{\rm LL}$ :

$$V_{\mathrm{L}}'(t) = V_{\mathrm{LL}}'(t) \tag{19}$$

$$V_{\rm L}'(t)=0\tag{20}$$

At this point, the loss caused by the load is negligible. However, the addition of the hysteresis module introduces additional loss. The voltage across the resistor  $V_{R_i}$  is:

$$V_{R_s}(t) = V_{\text{out}}(t) - V_{\text{ref}}(t) \tag{21}$$

The voltage across the series-connected resistors  $R_1$  and  $R_2$  is  $V_{R_1+R_2}$ :

$$V_{R_1+R_2}(t) = V_{\text{out}}(t) - V'_{\text{L}}(t)$$

(22)

$$V_{R_1+R_2}(t) = V_{\text{out}}(t)$$

(23)

The power supply voltage  $V_{\rm DD}$  of the comparator is the same as the output voltage  $V_{\rm out}$ :

$$V_{\rm DD}(t) = V_{\rm out}(t) \tag{24}$$

When the voltage  $V_{\text{out}}$  is set to 3.3 V and the hysteresis circuit is conducting, the maximum loss, across resistor  $R_1$ ,  $R_2$ ,  $R_3$  is:

$$P_{R_1 + R_2}(t) = \frac{V_{\text{out}}^2(t)}{R_1 + R_2} = 0.825 \ \mu\text{W}$$

(25)

$$P_{R_3}(t) = \frac{V_{R_3}^2(t)}{R_3} = \frac{\left[V_{\text{out}}(t) - V_{\text{ref}}(t)\right]^2}{R_3} = 2.1 \,\mu\text{W}$$

(26)

where is  $R_1 = 8.2 \text{ M}\Omega$ ,  $R_2 = 5 \text{ M}\Omega$ ,  $R_3 = 2 \text{ M}\Omega$ ,  $V_{\text{ref}} = 1.25 \text{ V}$ .

The loss generated by the reference voltage source is  $P_{\text{ref}}$ :

$$P_{\text{ref}}(t) = V_{\text{ref}}(t) \times I_{\text{ref}}(t) = 1.25 \,\mu\text{W}$$

(27)

Where  $I_{\rm ref}$  is the current flowing through the reference voltage source, the maximum current for the MAX6006 shunt reference voltage source is 1  $\mu$ A.

The loss generated by the comparator is:

$$P_{o}(t) = V_{out}(t) \times I_{o}(t) = 3.3 \,\mu\text{W}$$

(28)

where the quiescent current of the MCP6541 comparator is 1  $\mu A$  .

Therefore, the loss after adding the hysteresis module is  $P'_{loss}$ :

$$P'_{loss}(t) = P_{R_1 + R_2}(t) + P_{R_3}(t) + P_{ref}(t) + P_o(t) = 7.475 \text{ } \mu\text{W}$$

(29)

# Supplementary Table 1. Abbreviations and meanings appearing in the paper.

| Order | Full title                                                        | Abbreviation  |

|-------|-------------------------------------------------------------------|---------------|

| 1     | Triboelectric nanogenerator                                       | TENG          |

| 2     | Universal self-triggered passive output power management strategy | USPT-PMS      |

| 3     | Vertical contact-separation mode triboelectric nanogenerator      | CS-TENG       |

| 4     | Freestanding mode triboelectric nanogenerator                     | FS-TENG       |

| 5     | Output capacitor                                                  | $C_{ m out}$  |

| 6     | Input capacitor                                                   | $C_{ m in}$   |

| 7     | Parasitic capacitance in the load                                 | $C_{ m p}$    |

| 8     | Output capacitor terminal voltage                                 | $V_{ m out}$  |

| 9     | Low level output                                                  | $V_{ m OL}$   |

| 10    | High level output                                                 | $V_{ m OH}$   |

| 11    | Inherent capacitance                                              | $C_{ m o}$    |

| 12    | Freewheeling diode                                                | $D_5$         |

| 13    | Non-inverting terminal                                            | $V_{+}$       |

| 14    | Reference voltage                                                 | $V_{ m ref}$  |

| 15    | Load terminal voltage                                             | $V_{ m L}$    |

| 16    | Loss current                                                      | $I_{ m loss}$ |

| 17    | Inrush current                                                    | $I_{ m ir}$   |

| 18    | Load current                                                      | $I_{ m L}$    |

| 19    | High level output                                                 | $V_{ m LH}$   |

| 20    | Low level output                                                  | $V_{ m LL}$   |