Supplementary Information (SI) for Journal of Materials Chemistry C. This journal is © The Royal Society of Chemistry 2025

## **Supporting Information**

Arbitrary-Ordered Pulsed Programming Achieving 11 Well-Separated Programming Levels via a Multilevel Transistor–Memristor Series Configuration

Jing-Ci Gao<sup>1</sup>, Kuan-Han Lin<sup>2</sup>, Wei-Lun Chen<sup>2</sup>, Kai-Shin Hsu<sup>2</sup>, Chi-Chein Chen<sup>2</sup>, Jen-Sue Chen\*<sup>1,2</sup>

<sup>1</sup>Program on Semiconductor Packaging and Testing, Academy of Innovative Semiconductor and Sustainable Manufacturing, National Cheng Kung University Tainan 70101, Taiwan <sup>2</sup>Department of Materials Science and Engineering, National Cheng Kung University Tainan 70101, Taiwan

\* Corresponding author. E-mail: <u>jenschen@ncku.edu.tw</u>

**KEYWORDS:** Memristor, Multilevel resistive switching, Retention, endurance, Transistor—memristor configuration

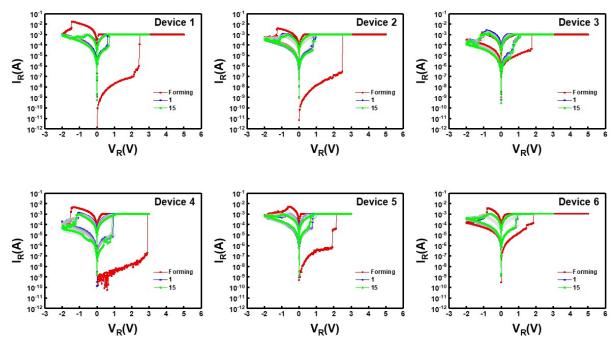

**Figure S1.** Device-to-device (D2D) I–V characteristics of Pt/Ta/ZrO<sub>x</sub>/Pt memristors (Device 1 to Device 6). Each cell underwent a forming process followed by 15 consecutive switching cycles. The consistent bipolar switching behavior and stable current levels confirm good D2D uniformity and operational reliability.

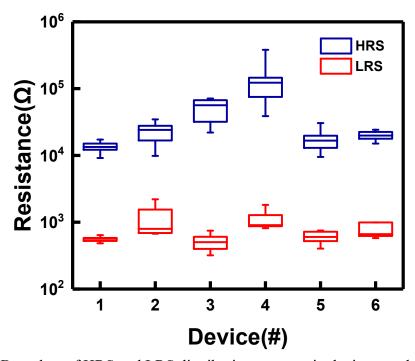

**Figure S2.** Box plots of HRS and LRS distributions across six devices, each measured over 15 switching cycles. The results reflect reasonable device-to-device variation and switching stability, supporting the reproducibility shown in Supplementary Figure S1.

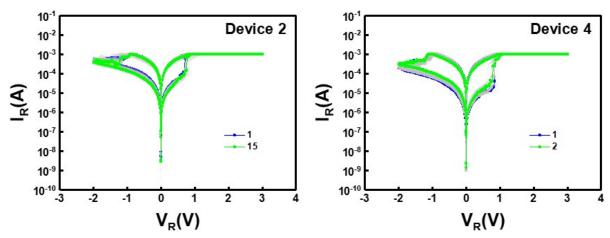

**Figure S3.** I–V characteristics of Device 2 and Device 4 remeasured after 50 days, showing stable resistive switching over 15 cycles. The preserved switching functionality confirms excellent environmental stability and long-term operational reliability of the devices.

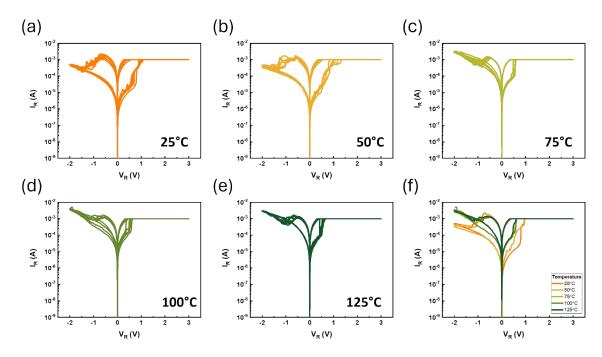

**Figure S4.** (a-e) Temperature-dependent I–V characteristics of the memristor measured at 25 °C, 50 °C, 75 °C, 100 °C and 125 °C under a fixed compliance current of 1 mA. (f) Overlap of representative I–V characteristics measured at 25 °C, 50 °C, 75 °C, 100 °C, and 125 °C.

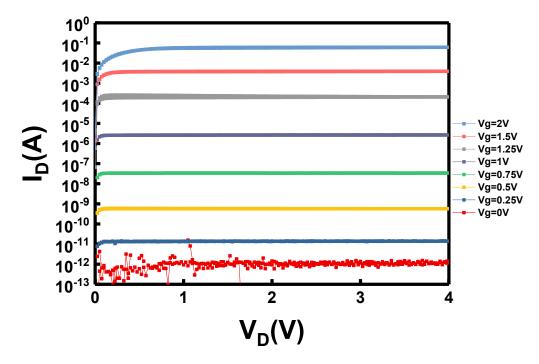

**Figure S5.** Transfer characteristics of the commercial NMOS transistor (2N7000). (a) Output curves under different  $V_g$  levels demonstrate well-controlled saturation current. This  $V_g$ -tunable current-limiting behavior enables the transistor to serve as an effective current compliance (CC) component during the SET process.

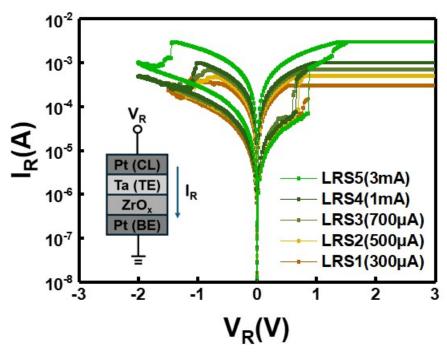

**Figure S6.** DC sweep curves of multilevel resistance states measured from a single memristor device under direct compliance current control. The linearity is highly consistent with that observed in the transistor–memristor series configuration, confirming that the current-limiting function does not distort intrinsic device behavior.

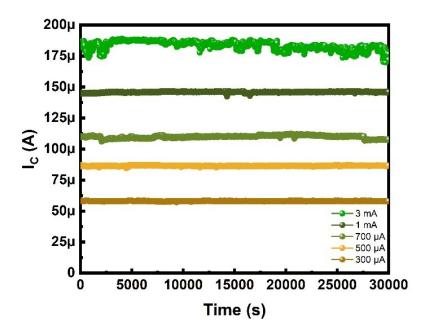

**Figure S7.** Retention performance of LRS1–LRS5 states measured on a single memristor at a read voltage of 0.1 V under 85 °C for 30,000 s, showing stable current without noticeable degradation, confirming excellent thermal stability and data retention capability.

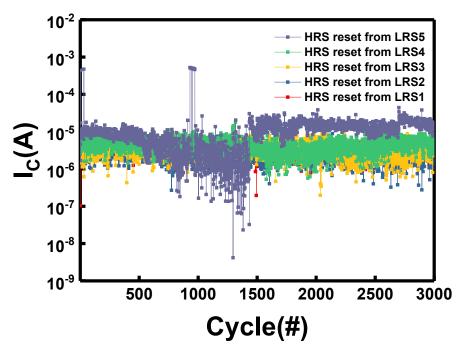

**Figure S8.** Endurance characteristics of HRS obtained from different initial LRS states (LRS1 to LRS5). The results demonstrate that the reset process consistently leads to a stable HRS, regardless of the preceding LRS, confirming the device's immunity to prior state history and its reliable switching repeatability.

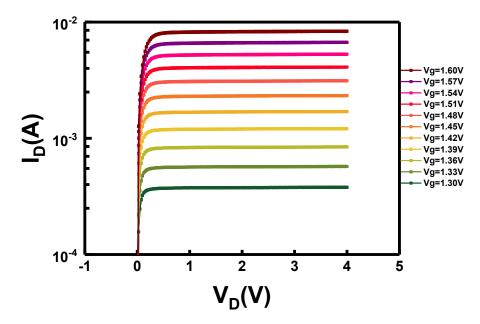

**Figure S9.**  $I_DV_D$  characteristics of the 2N7000 transistor measured under gradually increased gate voltages ( $V_g = 1.30$  to 1.60 V), corresponding to programmed level 1 to 11, showing distinct and well-separated current levels.

## Incremental Vg Device 1 Device 2 Device 3 Device 4 Device 5 Device 8 Device 6 Device 7 Device 9 Device 10 € 450 \_0 300 Program level Program level Decremental Vg Device 1 Device 2 Device 3 Device 4 Device 5 8 7 6 5 4 3 Program level Device 6 Device 7 Device 8 Device 9 Device 10

**Figure S10.** Statistical analysis of device-to-device (D2D) uniformity for 11 programmable levels measured from ten devices fabricated under identical conditions.

<u>300</u>

8 7 6 5 4 3 Program level

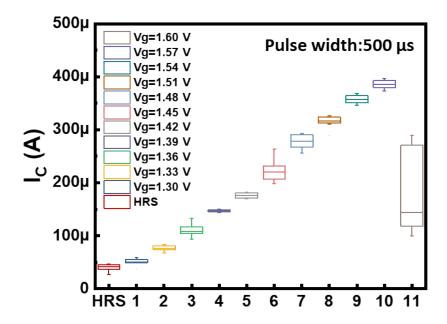

**Figure S11.** Box plot of read current distributions for 11 programmable levels obtained under a 500 μs pulse width. The results show ten well-defined low-resistance states and one high-resistance state (HRS).

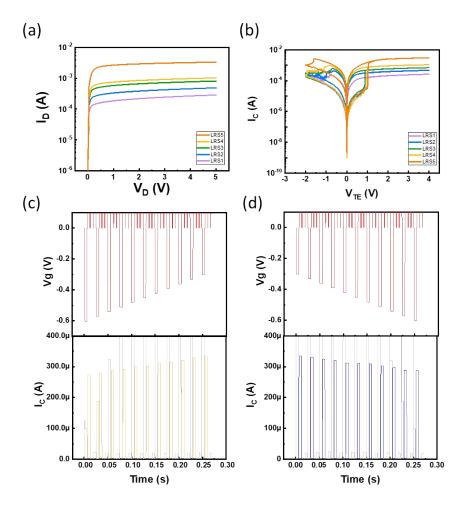

Figure S12. Validation of multilevel operation robustness using a commercial transistor (2SK170). (a)  $I_D$ - $V_D$  characteristics of the 2SK170 transistor measured under gradually increased gate voltages (Vg = -0.3 V, -0.46 V, -0.48 V, -0.53 V and -0.55 V), corresponding to programmed LRS1 to LRS5, showing distinct and well-separated current levels. (b) Multilevel resistance states (LRS) are achieved by varying the Vg of a series-connected 2N7000 transistor. The applied Vg are -0.3 V, -0.46 V, -0.48 V, -0.53 V and -0.55 V. (c, d) Incremental ( $-0.6 \rightarrow -0.3 \text{ V}$ ) and decremental ( $-0.3 \rightarrow -0.6 \text{ V}$ ) Vg programming schemes and their corresponding experimental results, showing the current responses  $I_C$  during programming and corresponding statistical distributions of the read currents for each level.

Table S1 HRS Current read at -0.1 V corresponding to different LRS states

| State         | HRS current@-0.1 V |  |  |

|---------------|--------------------|--|--|

| LRS5 (3mA)    | 7.34E-06 A         |  |  |

| LRS4 (1mA)    | 2.53E-06 A         |  |  |

| LRS3 (700 μA) | 5.28E-06 A         |  |  |

| LRS2 (500 μA) | 6.00E-06 A         |  |  |

| LRS1 (300 μA) | 3.46E-06 A         |  |  |

|               |                    |  |  |

$\label{eq:comparison} \textbf{Table S2} \ \ \text{Comparison of Transistor-Memristor Architectures for Multistate and } \ V_g$   $\ \ \text{Programming}$

| Device structure<br>(T+R)               | Number<br>of States | Retention             | Endurance | $ m V_g$ pulse programing | Bidirectional<br>Multistate | Ref.         |

|-----------------------------------------|---------------------|-----------------------|-----------|---------------------------|-----------------------------|--------------|

| 2N(7000)+<br>Pt/Ta/ZrO <sub>x</sub> /Pt | 8                   | > 10000 s<br>(25 °C)  | >3000     | <b>√</b>                  | <b>√</b>                    | This<br>work |

| NMOS+<br>Ta/TaO <sub>x</sub> /Pt        | 6                   | -                     | >106      | <b>√</b>                  | ×                           | [1]          |

| ITO/SiN/TaN<br>(Only R)                 | 8                   | > 10000 s<br>(25 °C)  | >1000     | -                         | <b>√</b>                    | [2]          |

| NMOS+<br>Ti/HfO <sub>2</sub> /TiN       | 6                   | > 10000 s<br>(125 °C) | $>5x10^5$ | ×                         | ×                           | [3]          |

| CMOS+<br>TiN/Ti/HfO <sub>2</sub> /TiN   | 9                   | -                     | 10        | ×                         | ×                           | [4]          |

| NMOS+<br>TiN/Ti/HfO <sub>2</sub> /TiN   | 9                   | -                     | -         | <b>√</b>                  | ×                           | [5]          |

## **Reference:**

- 1. E. J. Merced-Grafals, N. Dávila, N. Ge, R. S. Williams and J. P. Strachan, *Nanotechnol.*, 2016, **27**, 365202.

- 2. D. Ju, S. Kim and S. Kim, *Nanomater.*, 2023, **13**, 2477.

- 3. P.-H. Chen, Y.-T. Su, W.-C. Huang and C.-W. Wu, *IEEE Trans. Electron Devices*, 2023, **70**, 1014-1018.

- 4. E. P.-B. Quesada, T. Rizzi, A. Gupta, M. K. Mahadevaiah, A. Schubert, S. Pechmann, R. Jia, M. Uhlmann, A. Hagelauer and C. Wenger, 2023 14th Conference on Electron Devices (CDE), Spanish, 2023.

- 5. V. Milo, A. Glukhov, E. Pérez, C. Zambelli, N. Lepri, M. K. Mahadevaiah, E. P.-B. Quesada, P. Olivo, C. Wenger and D. Ielmini, *IEEE Trans. Electron Devices*, 2021, **68**, 3832-3837.