Supporting Information to:

## High-performance Top-gated Monolayer SnS<sub>2</sub> Field-effect Transistors and Their Integrated Logic Circuits

H. S. Song<sup>1, 2</sup>, S. L. Li<sup>1\*</sup>, L. Gao<sup>2</sup>, Y. Xu<sup>1</sup>, K. Ueno<sup>3</sup>, J.Tang<sup>2\*</sup>, Y. B. Cheng<sup>2, 4</sup>,

K.Tsukagoshi<sup>1\*</sup>

1. International Center for Materials Nanoarchitectonics (WPI-MANA), National Institute for Materials Science (NIMS), Tsukuba, Ibaraki 305-0044, Japan

2. Wuhan National Laboratory for Optoelectronics (WNLO) and School of Optical and Electronic Information, Huazhong University of Science and Technology (HUST), Wuhan 430074, P. R. China

3. Department of Chemistry, Graduate School of Science and Engineering, Saitama University, Saitama 338-8570, Japan

4. Department of Materials Engineering, Monash University, Melbourne, Victoria,3800, Australia

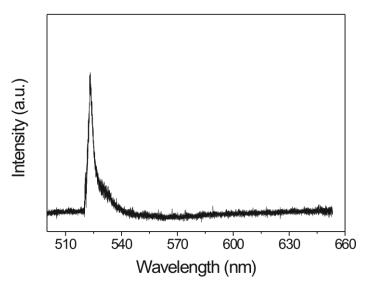

Figure S1. Micro-photoluminescence of single layer SnS<sub>2</sub> flake fabricated for TG-FET.

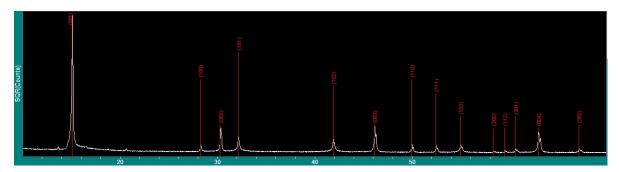

Figure S2. Powder XRD of  $SnS_2$  bulks, red lines denote from the standard card and the white peaks correspond to XRD data. The exfoliated source demonstrates pure hexagonal  $SnS_2$  with JCPDS NO.83-1706.

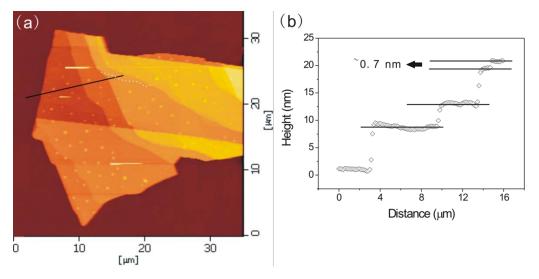

Fig.S3 (a,b) AFM image of multiple layer  $SnS_2$  flake and its height profile along the black line. The white dotted line shows the boundary of two neighbor layers and the height difference is ~0.7 nm. The 0.7 nm scanning demonstrate that our AFM instruments can identify monolayer scanning.

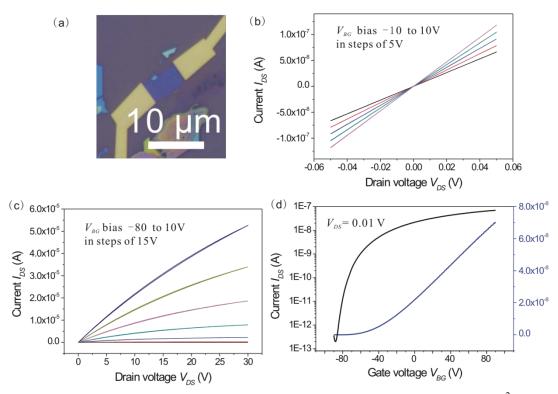

Figure S4. BG-FET performances with bare top surface, the carrier mobility is ~10 cm<sup>2</sup>/Vs. For the calculation to the BG-FET mobility: The BG-FET was measured in standard back-gated FET structure utilizing 285 nm SiO<sub>2</sub> covering layer with bare SnS<sub>2</sub> flake top surface as the channel. For the calculation of mobility, we utilize the linear working zone of FET as

$$\mu_{BG} = g_{m} \times \frac{L}{W} \times \frac{1}{C_{i}} \times \frac{1}{V_{DS}}$$

, while the transconductance  $g_{m} = \frac{dI_{DS}}{dV_{BG}}$  was extracted from Fig.

S2d,  $g_m=8\times10^{-10}$  A/V; the capacitance per unit area of SiO<sub>2</sub>,  $C_i=\varepsilon_0\varepsilon_r/d = 8.85\times10^{-12}$ F/m×3.9 /(285×10<sup>-9</sup> m)=1.21×10<sup>-8</sup> F/cm<sup>2</sup>; The ratio of channel length to width is ~5/3. Substituting all the

above data, we can get  $\mu_{BG} = g_{m} \times \frac{L}{W} \times \frac{1}{C_{i}} \times \frac{1}{V_{DS}} = 8 \times 10^{-10} \times \frac{5}{3} \times \frac{1}{1.21 \times 10^{-8}} \times 100 \text{ cm}^{2}/\text{Vs}$

$\sim 10 \text{ cm}^2/\text{Vs}.$

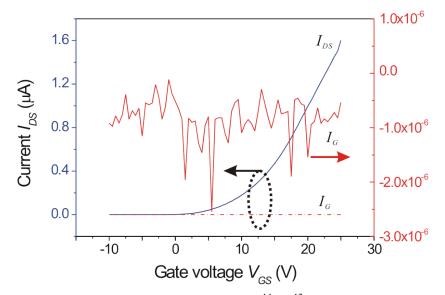

**Figure S5**. Leakage current ( $I_G$ ) stands in the order of  $10^{-14}$ - $10^{-12}$  ampere during our measurement.