**Electronic Supplementary Information**

## Coupled self-assembled monolayer for enhancement of Cu diffusion barrier and adhesion properties

Yongwon Chung,<sup>†a</sup> Sanggeun Lee,<sup>†a</sup> Chandreswar Mahata,<sup>a</sup> Jungmok Seo,<sup>a</sup> Seung-Min Lim,<sup>b</sup> Min-su Jeong,<sup>c</sup> Hanearl Jung,<sup>d</sup> Young-Chang Joo,<sup>b</sup> Young-Bae Park,<sup>c</sup> Hyungjun Kim,<sup>d</sup> and Taeyoon Lee<sup>\*a</sup>

<sup>a</sup>Nanobio Device Laboratory, School of Electrical and Electronic Engineering, Yonsei University, 50 Yonsei-ro, Seodaemun-gu, Seoul 120-749, Republic of Korea. E-mail: taeyoon.lee@yonsei.ac.kr

<sup>b</sup>Nanodevice Materials Laboratory, Department of Materials Science & Engineering, Seoul National University, 1 Gwanak-ro, Gwanak-gu, Seoul 151-744, Republic of Korea

<sup>c</sup>School of Materials Science and Engineering, Andong National University, 1375 Gyeongdongro, Andong-si, Gyeongsangbuk-do 760-749, Republic of Korea

<sup>d</sup>Nanodevice Laboratory, School of Electrical and Electronic Engineering, Yonsei University, 50 Yonsei-ro, Seodaemun-gu, Seoul 120-749, Republic of Korea

<sup>†</sup> These authors contributed equally as first authors.

\* Corresponding author:

Tel: +82-2-2123-5767

Fax: +82-2-313-2879

e-mail address: taeyoon.lee@yonsei.ac.kr

1

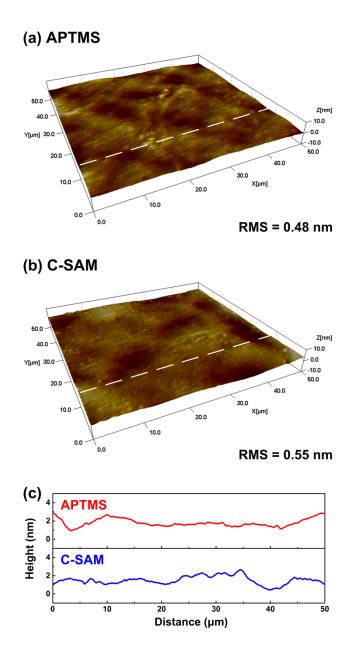

**Fig. S1** AFM images of the substrates coated with (a) APTMS and (b) C-SAM and their (c) cross-sectional image obtained from a larger scale.

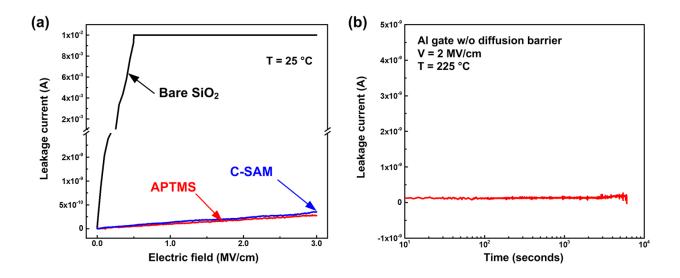

**Fig. S2** (a) Representative leakage current versus electric field results of the fabricated MOS capacitors using no diffusion barrier, APTMS, and C-SAM. (b) TDDB test results without diffusion barrier while using Al gate at 225 °C and 2 MV/cm.