**Electronic Supplementary Information**

## Low-temperature annealed PbS quantum dot films for scalable and flexible ambipolar thin-film-transistors and circuits

Chan Ho Jo,<sup>*a*+</sup> Jae Hyun Kim,<sup>*b*+</sup> Jaekyun Kim,<sup>*b*</sup> Jiwan Kim,<sup>*c*</sup> Min Suk Oh,<sup>*c*</sup> Moon Sung Kang,<sup>*d*</sup> Myung-Gil Kim,<sup>*e*</sup> Yong-Hoon Kim,<sup>*f*</sup> Byeong-Kwon Ju<sup>*a*\*</sup> and Sung Kyu Park<sup>*b*\*</sup>

<sup>a</sup> Department of Micro/Nano Systems, Korea University, Seoul 136-701, Korea.

<sup>b</sup> School of Electrical and Electronics Engineering, Chung-Ang University, Seoul 156-756, Korea.

<sup>c</sup> Flexible Display Research Center, Korea Electronics Technology Institute, Seongnam 463-816, Korea.

<sup>d</sup> Department of Chemical Engineering, Soongsil University, Seoul 156-743, Korea.

<sup>e</sup> Department of Chemistry, Chung-Ang University, Seoul 156-756, Korea.

<sup>*f*</sup> School of Advanced Materials Science and Engineering, and SKKU Advanced Institute of Nanotechnology (SAINT), Sungkyunkwan University, Suwon 440-746, Korea.

E-mail: <u>skpark@cau.ac.kr</u> (S. K. Park), <u>bkju@korea.ac.kr</u> (B. -K. Ju)

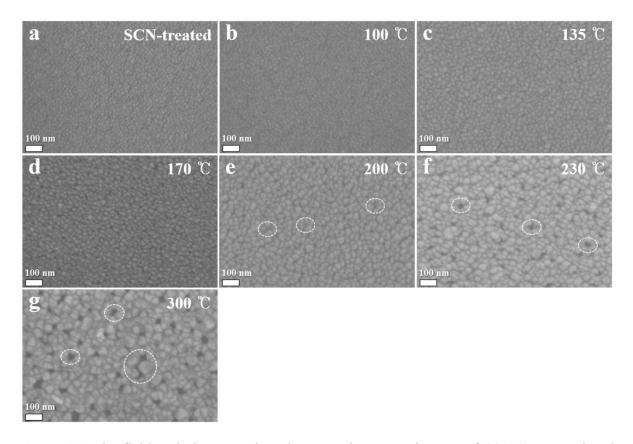

**Figure S1.** The field-emission scanning electron microscope images of (a) SCN-treated and then (b-g) thermally annealed PbS QD films. The white dotted circles in the pictures indicate examples of the voids (or disconnection) caused by aggregation (sintering) of QDs due to high temperature annealing. Above 200 °C, the number and the size of voids gradually increased with increasing  $T_a$ .

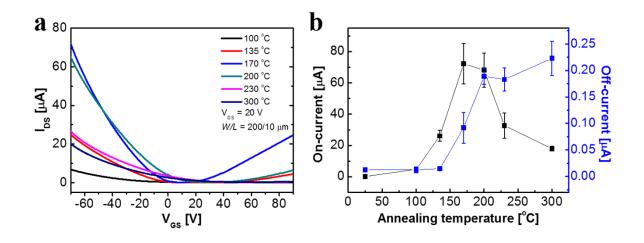

**Figure S2**. (a) Temperature-dependent linear scale of  $I_{DS}$ - $V_{GS}$  transfer characteristics up to 300 °C and (b) temperature-dependent p-type on-/off- currents of SCN- and thermal-treated PbS QD TFTs with Au S/D electrodes (at  $V_{DS} = 20$  V). The error bars indicate the standard deviation of ten devices for the p-type on-/off- currents.

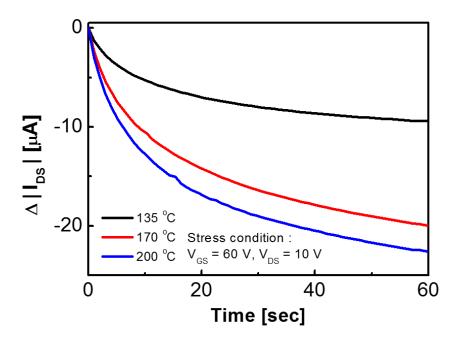

Figure S3. The variation of  $I_{DS}$  of SCN- and thermal-treated PbS QD TFTs with continuous bias stress ( $V_{GS} = 60$  V and  $V_{DS} = 10$  V).

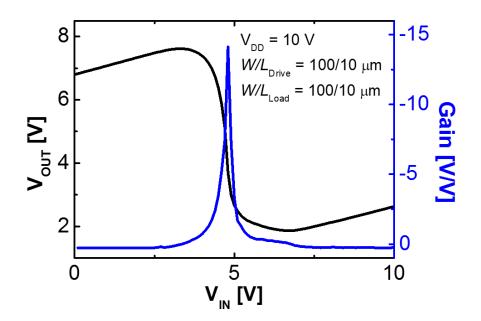

**Figure S4.** The transfer and gain characteristics of a CMOS inverter operating at  $V_{DD}$  of +10 V using SCN-treated and 170 °C-annealed PbS QD TFTs on ultra-thin PI. A  $\beta$ -ratio is 1 with  $(W/L)_{\text{Load, Drive}}$  of 100  $\mu$ m /10  $\mu$ m and a gain of this device is approximately 14.1 V/V.

**Table S1**. The Scherrer equation-based grain size analysis from GIAXRD peak at  $2\theta = 30.1^{\circ}$  in Figure 3c.

|                    | SCN-<br>treated | 100 °C | 135 °C | 170 °C | 200 °C | 230 °C | 300 °C |

|--------------------|-----------------|--------|--------|--------|--------|--------|--------|

| grain size<br>[nm] | 5.7             | 6.4    | 8.6    | 11     | 13.1   | 14     | 17.2   |